# 1000BASE-T/100BASE-TX/10BASE-T Physical Layer Compliance Tests Manual

June 2006

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

IMPORTANT - PLEASE READ BEFORE INSTALLING OR USING INTEL® PRE-RELEASE PRODUCTS

Please review the terms at <a href="http://www.intel.com/netcomms/prerelease\_terms.htm">http://www.intel.com/netcomms/prerelease\_terms.htm</a> carefully before using any Intel® pre-release product, including any evaluation, development or reference hardware and/or software product (collectively, "Pre-Release Product"). By using the Pre-Release Product, you indicate your acceptance of these terms, which constitute the agreement (the "Agreement") between you and Intel Corporation ("Intel"). In the event that you do not agree with any of these terms and conditions, do not use or install the Pre-Release Product and promptly return it unused to Intel.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

The NAME OF PRODUCT may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See <a href="http://www.intel.com/products/ht/Hyperthreading\_more.htm">http://www.intel.com/products/ht/Hyperthreading\_more.htm</a> for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright  $\ensuremath{\mathbb{C}}$  2006, Intel Corporation. All Rights Reserved.

# **Revision History**

| Date      | Revision | Description                                                                                                                                                                                                                                                                                           |  |

|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| May 2006  | 4.3      | Revised document with new Intel branding documentation templates.                                                                                                                                                                                                                                     |  |

| Oct. 2005 | 4.2      | placed references to PhyConf tool with LANConf tool.                                                                                                                                                                                                                                                  |  |

| June 2005 | 4.1      | Replaced references to GigConf tool with LANConf tool.                                                                                                                                                                                                                                                |  |

| Feb. 2005 | 4.0      | Updated the BER formula.  Added a note to step 4 of Section 3.5 explaining how to measure droop across points F/G or H/J.  Removed "100 Ohm Resistive Load" from Text Fixture 40-32 in Section 7.5.                                                                                                   |  |

| Sep. 2004 | 3.9      | Removed references to "BER Test User's Guide." This document does not exist.                                                                                                                                                                                                                          |  |

| Nov. 2003 | 3.8      | Minor edits.                                                                                                                                                                                                                                                                                          |  |

| Oct. 2003 | 3.7      | Minor edits.                                                                                                                                                                                                                                                                                          |  |

| Sep. 2003 | 3.5      | lore updates for IEEE Gigabit Ethernet testing.                                                                                                                                                                                                                                                       |  |

| Aug. 2003 | 3.0      | eneral updates for IEEE Gigabit Ethernet testing.                                                                                                                                                                                                                                                     |  |

| Aug. 2002 | 2.0      | General edits and additional information included in Appendix C.                                                                                                                                                                                                                                      |  |

| Dec. 2001 | 1.2      | Listed required versus recommended tests in Sections 1.1.1 and 1.1.2.  Added new section for alien crosstalk noise rejection test.  Included diagrams for test fixtures in Appendix A.  Changed Appendix C from "Calculations for Worst-Case Gigabit Cable" to "Worst-Case Cable for Gigabit Jitter." |  |

| Aug. 2001 | 1.1      | Changed GT.exe software name to GigConf.exe.                                                                                                                                                                                                                                                          |  |

| June 2001 | 1.0      | First release.                                                                                                                                                                                                                                                                                        |  |

## **Contents**

| 1 | Intr | oduction                                                     | 6               |

|---|------|--------------------------------------------------------------|-----------------|

|   | 1.1  | Reference Documents                                          | 6               |

|   | 1.2  | Basic Concepts                                               | 6               |

|   |      | 1.2.1 Calibration                                            |                 |

|   |      | 1.2.2 Triggering                                             | 7               |

|   |      | 1.2.2.1 Signal with an Ambiguous Trigger Level               | 7               |

|   |      | 1.2.2.2 Signal Does Not Appear                               |                 |

|   | 4.0  | 1.2.3 Displaying Waveforms                                   |                 |

|   | 1.3  | Required Test Equipment                                      |                 |

|   | 1.4  | Required Test Fixtures                                       |                 |

|   | 1.5  | Required Software and Data Patterns                          |                 |

|   | 1.6  | PHY Conformance Tests                                        |                 |

| 2 | 1000 | OBASE-T Peak Differential Output Voltage and Level Accuracy  |                 |

|   | 2.1  | Test Purpose                                                 |                 |

|   | 2.2  | Specification                                                |                 |

|   | 2.3  | Test Equipment                                               |                 |

|   | 2.4  | Test Fixtures                                                |                 |

|   | 2.5  | Test Procedure                                               | 15              |

| 3 | 1000 | OBASE-T Maximum Output Droop                                 | 20              |

|   | 3.1  | Test Purpose                                                 | 20              |

|   | 3.2  | Specification                                                | 20              |

|   | 3.3  | Test Equipment                                               | 20              |

|   | 3.4  | Test Fixtures                                                |                 |

|   | 3.5  | Test Procedure                                               | 21              |

| 4 | 1000 | OBASE-T Receiver Differential Input Signals (Bit Error Rate) | 24              |

|   | 4.1  | Test Purpose                                                 | 24              |

|   | 4.2  | Specification                                                |                 |

|   | 4.3  | Test Equipment                                               | 24              |

|   | 4.4  | Test Fixtures                                                | 24              |

|   | 4.5  | Test Procedure                                               |                 |

|   | 4.6  | Calculating Bit Error Rate (BER)                             | 25              |

| 5 | 1000 | OBASE-T Alien Crosstalk Noise Rejection                      | 26              |

|   | 5.1  | Test Purpose                                                 |                 |

|   | 5.2  | Specification                                                |                 |

|   | 5.3  | Test Equipment                                               |                 |

|   | 5.4  | Test Fixtures                                                | 26              |

|   | 5.5  | Test Procedure                                               | 26              |

| 6 | 1000 | OBASE-T MDI Return Loss                                      | 28              |

|   | 6.1  | Test Purpose                                                 |                 |

|   | 6.2  | Specification                                                |                 |

|   | 6.3  | Test Equipment                                               |                 |

|   | 6.4  | Test Fixtures                                                |                 |

|   | 6.5  | Test Procedure                                               | 28              |

| 7 | 1000 | OBASE-T MDI Common-Mode Output                               | 32              |

| • | 7.1  | Test Purpose                                                 |                 |

|   | 7.1  | Specification                                                |                 |

|   | 7.2  | Test Equipment                                               |                 |

|   | 7.4  | Test Fixtures                                                |                 |

|   |      |                                                              | · · · · · · • = |

|    | 7.5                                  | Test Procedure                                            | 32                   |

|----|--------------------------------------|-----------------------------------------------------------|----------------------|

| 8  | 100B <i>A</i>                        | ASE-TX Differential Output Voltage (UTP)                  | 36                   |

|    | 8.1<br>8.2                           | Test Purpose Specification                                | 36<br>36             |

|    |                                      | Test Equipment                                            |                      |

|    |                                      | Test Procedure                                            |                      |

| 9  |                                      | ASE-TX Waveform Overshoot                                 |                      |

| 7  |                                      | Test Purpose                                              |                      |

|    |                                      | Specification                                             |                      |

|    |                                      | Test Equipment                                            |                      |

|    |                                      | Test Fixtures                                             |                      |

|    | 9.5                                  | Test Procedure                                            | 43                   |

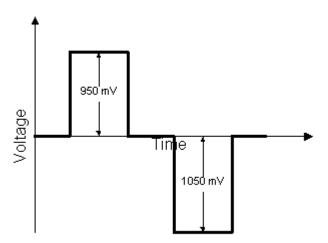

| 10 | 100Ba                                | ase-TX Signal Amplitude Symmetry                          | 46                   |

|    |                                      | Test Purpose                                              |                      |

|    |                                      | Specification                                             |                      |

|    |                                      | Test Procedure                                            |                      |

| 11 |                                      | ase-TX Transmitter Return Loss                            |                      |

|    |                                      | Test Purpose                                              |                      |

|    |                                      | Specification                                             |                      |

|    |                                      | Test Equipment                                            |                      |

|    |                                      | Test Procedure                                            |                      |

| 12 |                                      | ase-TX Rise and Fall Times                                |                      |

| 12 |                                      | Test Purpose                                              |                      |

|    |                                      | Specification                                             |                      |

|    |                                      | Test Equipment                                            |                      |

|    |                                      | Test Fixtures                                             |                      |

|    | 12.5                                 | Test Procedure                                            | 53                   |

| 13 |                                      | ase-TX Duty Cycle Distortion (DCD)                        |                      |

|    |                                      | Test Purpose                                              |                      |

|    |                                      | Specification                                             |                      |

|    |                                      | Test Equipment                                            |                      |

|    |                                      | Test Procedure                                            |                      |

| 14 |                                      | ase-TX Transmit Jitter                                    |                      |

| 14 |                                      | Test Purpose                                              |                      |

|    |                                      | Specification                                             |                      |

|    |                                      | Test Equipment                                            |                      |

|    |                                      | Test Fixtures                                             |                      |

|    | 14.5                                 | Test Procedure                                            | 64                   |

| 15 | 100Ba                                | ase-TX Differential Input Signals (BER)                   | 66                   |

|    | 15.1                                 | Test Purpose                                              | 66                   |

|    |                                      | ·                                                         |                      |

|    | 15.2                                 | Specification                                             | 66                   |

|    | 15.2<br>15.3                         | Specification                                             | 66                   |

|    | 15.2<br>15.3<br>15.4                 | Specification. Test Equipment. Test Fixtures              | 66                   |

|    | 15.2<br>15.3<br>15.4<br>15.5         | Specification                                             | 66                   |

| 16 | 15.2<br>15.3<br>15.4<br>15.5<br>15.6 | Specification Test Equipment Test Fixtures Test Procedure | 66<br>66<br>66<br>67 |

|    | 16.2 Specification                                                      |    |

|----|-------------------------------------------------------------------------|----|

|    | 16.3 Test Equipment                                                     |    |

|    | 16.4 Test Fixtures                                                      |    |

|    | 16.5 Test Procedure                                                     | 68 |

| 17 | 10Base-T Peak Differential Output Voltage on TD Circuit                 | 72 |

|    | 17.1 Test Purpose                                                       |    |

|    | 17.2 Specification                                                      |    |

|    | 17.3 Test Equipment                                                     |    |

|    | 17.4 Test Fixtures                                                      |    |

|    | 17.5 Test Procedure                                                     | 72 |

| 18 | 10Base-T Harmonic Content                                               | 76 |

|    | 18.1 Test Purpose                                                       |    |

|    | 18.2 Specification                                                      |    |

|    | 18.3 Test Equipment                                                     |    |

|    | 18.4 Test Fixtures                                                      |    |

|    | 18.5 Test Procedure                                                     |    |

| 40 |                                                                         |    |

| 19 | 10Base-T TD Circuit Impedance<br>(Transmitter Return Loss)              | 70 |

|    | ·                                                                       |    |

|    | 19.1 Test Purpose                                                       |    |

|    | 19.3 Test Equipment                                                     |    |

|    | 19.4 Test Equipment                                                     |    |

|    | 19.5 Test Procedure                                                     |    |

|    |                                                                         |    |

| 20 | 10Base-T TD Circuit Common-Mode Output Voltage                          |    |

|    | 20.1 Test Purpose                                                       |    |

|    | 20.2 Specification                                                      |    |

|    | 20.3 Test Equipment                                                     |    |

|    | 20.4 Test Fixtures                                                      |    |

|    | 20.5 Test Procedure                                                     | 80 |

| 21 | 10Base-T Transmitter Output Timing                                      |    |

|    | Jitter with Cable Model                                                 |    |

|    | 21.1 Test Purpose                                                       |    |

|    | 21.2 Specification                                                      |    |

|    | 21.3 Test Equipment                                                     |    |

|    | 21.4 Test Fixtures                                                      |    |

|    | 21.5 Test Procedure                                                     | 84 |

| 22 | 10Base-T Transmitter Output Timing Jitter without Cable Model           | 88 |

|    | 22.1 Test Purpose                                                       | 88 |

|    | 22.2 Specification                                                      | 88 |

|    | 22.3 Test Equipment                                                     |    |

|    | 22.4 Test Fixtures                                                      |    |

|    | 22.5 Test Procedure                                                     | 88 |

| 23 | 10Base-T RD Receiver Circuit Signal Acceptance Test (BER)               | 92 |

|    | 23.1 Test Purpose                                                       |    |

|    | 23.2 Specification                                                      |    |

|    | 23.3 Test Equipment                                                     |    |

|    | 23.4 Test Fixtures                                                      |    |

|    | 23.5 Test Procedure                                                     |    |

|    | 23.6 Calculating Bit Error Rate (BER)                                   | 93 |

| 24 | 10Base-T RD Circuit Differential Input Impedance (Receiver Return Loss) | 94 |

INTEL CONFIDENTIAL

|   | 24.1<br>24.2<br>24.3 | Test Purpose Specification Test Equipment                        | 94  |

|---|----------------------|------------------------------------------------------------------|-----|

|   | 24.3                 | Test Fixtures                                                    |     |

|   | 24.5                 | Test Procedure                                                   | 94  |

| Α |                      | Base-T Test Fixtures and Calibration Load Fixtures               |     |

|   | A.1                  | Fixture 40-25                                                    |     |

|   | A.2<br>A.3           | Fixture 40.6.1.1.1.A - Differential Breakout Cable               |     |

|   | A. 3<br>A. 4         | Fixture 40.8.3.1.A                                               |     |

|   | A.5                  | Fixture 40.8.3.1.B                                               |     |

|   | A.6                  | Fixture 40.8.3.1.C                                               |     |

|   | A.7                  | Fixture 40-28A                                                   |     |

|   | A.8                  | Fixture 40-28B                                                   | 102 |

|   | A.9                  | Fixture 40-32                                                    | 103 |

| В | Test                 | Fixture Construction Tips and Information                        | 106 |

|   | B.1                  | General Test Fixture Construction Guidelines                     |     |

|   | B.2                  | RJ-45 Connector Pin-Out, and Ethernet Cable Wire Assignment      | 106 |

| С | Wors                 | st-Case Cable for Jitter                                         | 108 |

|   | C.1                  | Constructing the 120-ohm Impedance Segments (L1 and L3)          | 100 |

|   |                      |                                                                  |     |

| D |                      | r Test Fixtures                                                  |     |

|   | D.1                  | 100 Ohm UTP Test Load                                            |     |

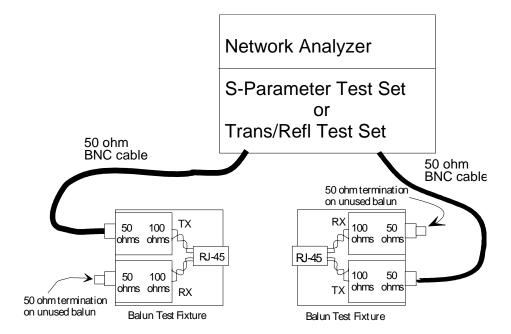

|   | D.2<br>D.3           | 100Base-TX Balun Test Fixture                                    |     |

|   | D.3<br>D.4           | Receiver Common-Mode Rejection Test Fixture                      |     |

|   | D.4<br>D.5           | 10Base-T Balun Test Fixture                                      |     |

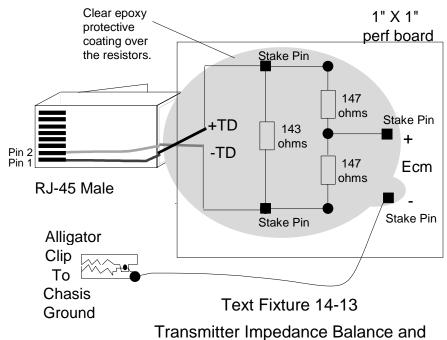

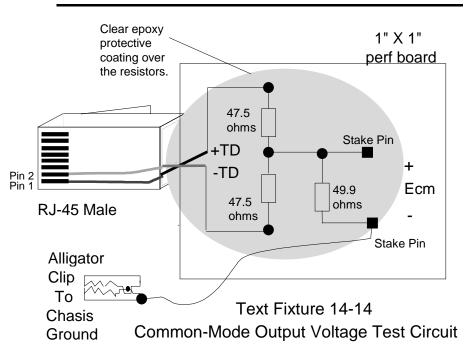

|   | D.6                  | Common-Mode Output Voltage Test Circuit (Fixture 14-14)          |     |

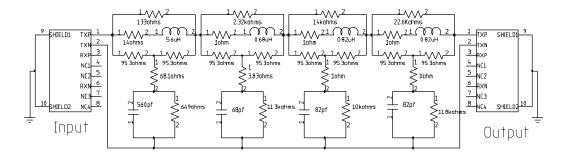

|   | D.7                  | 10BASE-TX 14_7 Twisted-Pair Model                                |     |

| E | Build                | ling and Testing UTP LAN Cables to Insertion Loss Specifications | 118 |

|   | E.1                  | Purpose                                                          |     |

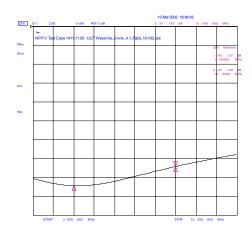

|   | E.2                  | Network Analyzer Setup and Calibration                           |     |

|   | E.3                  | Measuring the Insertion Loss of the Twisted Pair Cable           | 119 |

|   | E.4                  | Alternate Insertion Loss Measurement Techniques                  | 120 |

| F |                      | cing Measurement Error by Avoiding Cable Bending                 |     |

| G | Trou                 | bleshooting Guide                                                | 126 |

|   | G.1                  | Test Problems                                                    |     |

|   |                      | G.1.1 Oscilloscope Setups                                        |     |

|   |                      | G.1.2 Network Analyzer Setups                                    |     |

|   | G.2                  | Conformance Problems                                             | 127 |

|   | G.3                  | Differential Output Voltage (UTP) (ANSI specification 9.1.2.2)   | 127 |

|   | G.4                  | Overshoot (ANSI specification 9.1.3)                             |     |

|   | G.5                  | Amplitude Symmetry (ANSI specification 9.1.4)                    |     |

|   | G.6                  | Return Loss (ANSI specifications 9.1.5 and 9.2.2)                |     |

|   | G.7                  | Rise and Fall Times (ANSI specification 9.1.6)                   |     |

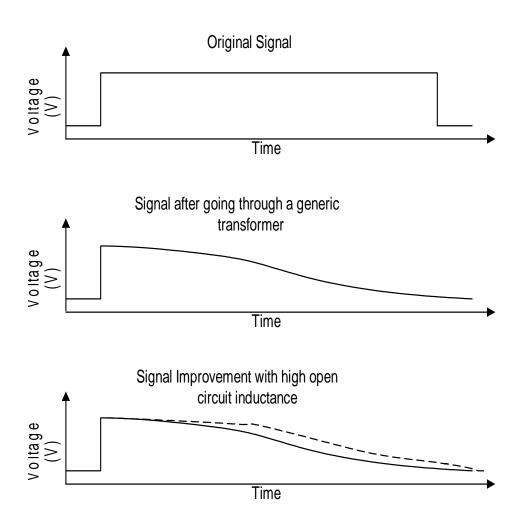

|   | G.8                  | Open Circuit Inductance (ANSI specification 9.1.7)               | 129 |

|   | G.9                  | Duty Cycle Distortion (ANSI specification 9.1.8)                 | 130 |

|   | G.10                 | Transmit Jitter (ANSI specification 9.1.9)                       |     |

|   | G.11                 | Differential Input Signals (ANSI specification 9.2.1)            | 132 |

|       | (ANSI specif  | mmon Mode Rejection<br>fication 9.2.3)        | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|---------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manu  | al Register   | Settings                                      | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| H.1   |               | 32546 Families                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| H.2   |               | 32547 Families                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| H.3   |               | ly                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 100R  | ase_TX Test   | Procedure for the                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I.1   | •             | 1                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| l.2   |               | Jsed for This Procedure                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.3   |               | n 9.1.2.2 - Differential Output Voltage (UTP) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               | Case                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               | Purpose                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               | cification                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.3.4 | Test Equipm   | nent                                          | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | I.3.5 Test    | Fixtures                                      | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.3.6 |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4   | Specification | n 9.1.6 - Rise/Fall Times                     | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | I.4.1 Test    | : Purpose                                     | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | 1.4.2 Spec    | cification                                    | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4.4 |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | I.4.5 Test    | : Procedure                                   | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.5   |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |               |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | I.5.8 Duty    | y Cycle Distortion Data                       | 155                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       | 1.3.6         | I.3.4 Test Equipm                             | I.3.4 Test Equipment I.3.5 Test Fixtures I.3.6 Test Procedure I.4 Specification 9.1.6 - Rise/Fall Times I.4.1 Test Purpose I.4.2 Specification I.4.3 Test Equipment I.4.4 Test Fixtures I.4.5 Test Procedure I.4.6 Notes for Using Pulse-Width Triggering I.4.7 10% and 90% of Positive Peak Voltage Calculations I.4.8 9.1.6 Rise and Fall Times I.5 Specification 9.1.8 - Duty Cycle Distortion (DCD) I.5.1 Test Case I.5.2 Test Purpose I.5.3 Specification I.5.4 Test Equipment I.5.5 Test Fixtures I.5.6 Test Procedure I.5.6 Test Procedure I.5.7 Generic Oscilloscope Settings |

### 1 Introduction

Networking is complex and involves a combination of advanced analog and digital technologies. To insure interoperability of networking solutions from various manufacturers, it is imperative that standard compliance testing is performed.

This document describes procedures for basic 1000BASE-T, 100BASE-TX, and 10BASE-T PHY compliance testing on Intel-based networking solutions. It does not include the complete set of tests required for TP-PMD conformance. However, it does include a recommended subset of these tests. After completing the test procedures described in this manual, the user should be able to identify and understand how to correct areas where the Unit Under Test (UUT) fails to conform to the standards listed in Section 1.1.

The procedures in this document are not intended to be specific to a particular manufacturer's test equipment. Moreover, they do not encompass all methods that a test may be performed. The tester is assumed to have a basic knowledge of oscilloscopes, network analyzers, signal generators, etc. Advice for success in obtaining accurate measurements are included throughout the document in shaded boxes.

The test methods described in this document have been customized to test Intel networking silicon only. Results may vary if these procedures are used on other manufacturers' networking devices.

### 1.1 Reference Documents

IEEE Standard 802.3-2000, Supplement to Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications:

- Sections 40.6 4.8 for 1000BASE-T

- Section 14.3 for 10BASE-T)

- ANSI X3.263-1995, Section 9 for 100BASE-TX

- ANSI Standard 802.3-25.4-2002

### 1.2 Basic Concepts

Recommended equipment settings are provided for each test procedure. These settings provide a good starting point for measurement. Variations in equipment can effect the resolution and accuracy of a signal. User experience manipulating equipment trigger and display can also effect the perception and interpretation of the waveform. In addition, probe polarity and trigger polarity can effect the interpretation of the signals. The settings provided are based on the test equipment used and may vary depending on equipment.

### 1.2.1 Calibration

Due to the precise measurements required for compliance testing, accurate measurement instruments are required. All equipment used during the testing process must be properly calibrated. Oscilloscopes must have a signal path compensation and probe calibration completed prior to testing.

### 1.2.2 Triggering

Determining the appropriate trigger point can mean the difference between passing and failing the physical layer conformance tests. Triggering guidelines are provided throughout this document and provide a good starting point for measurement. Fine tuning adjustments may be necessary in order to achieve the best display.

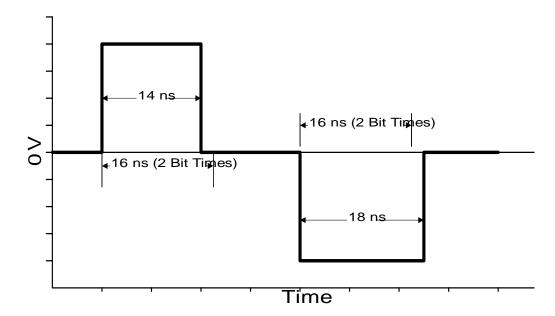

### 1.2.2.1 Signal with an Ambiguous Trigger Level

An ambiguous trigger level (either width or height) can prevent a stable display.

- 1. Try to reduce the delta between the minimum and maximum pulse widths as much as possible.

- 2. Determine where the trigger level falls on the waveform.

If the line passes through more than one point on the rising edge of the waveform, raise or lower the trigger until a point is found that is unambiguous as illustrated in Figure 1-1.

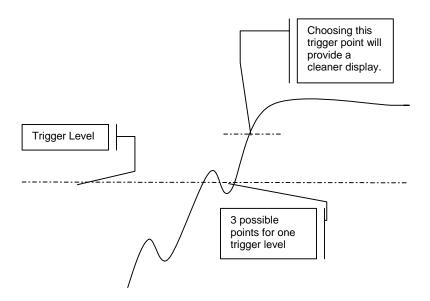

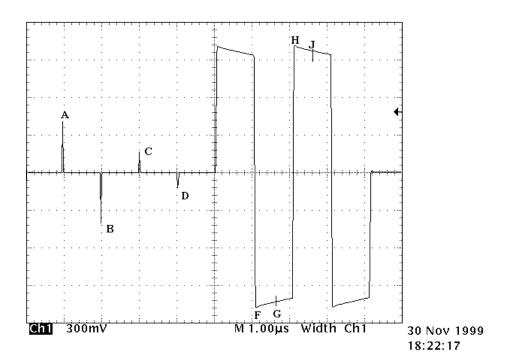

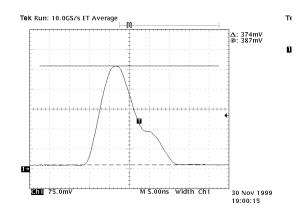

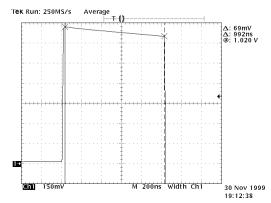

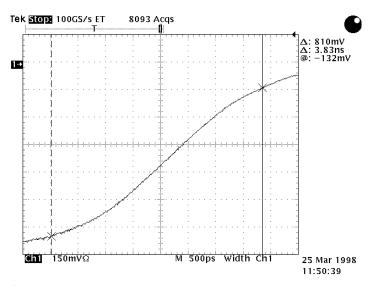

Figure 1-1. Ambiguous Trigger Level

### 1.2.2.2 Signal Does Not Appear

If the signal does not appear or appears only for an instant, the trigger level may be too high. Reducing the trigger level should cause the signal to appear (or re-appear).

### 1.2.3 Displaying Waveforms

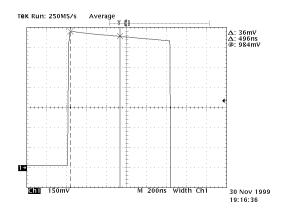

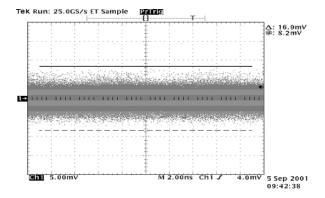

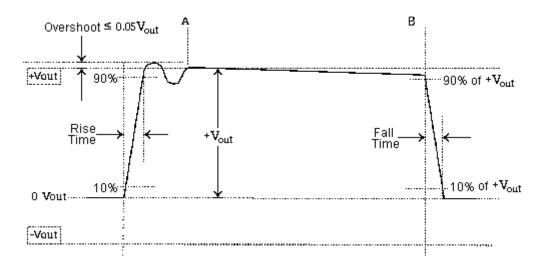

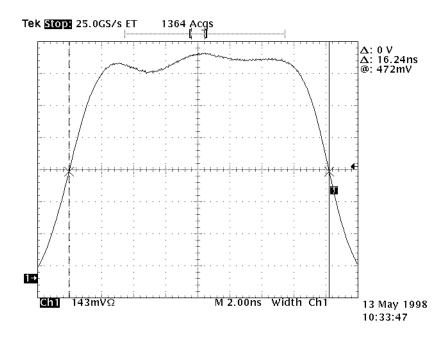

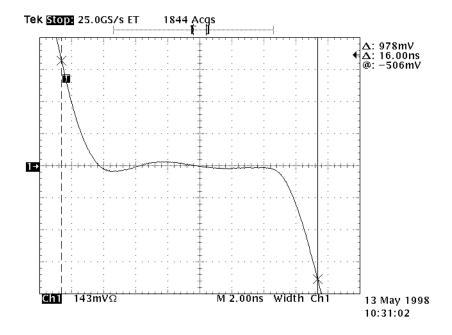

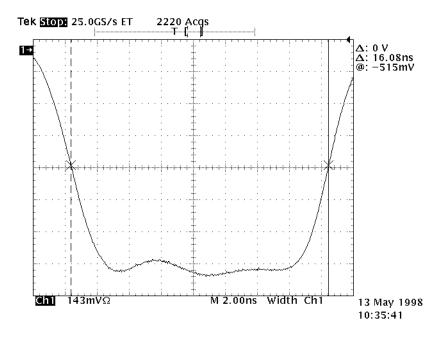

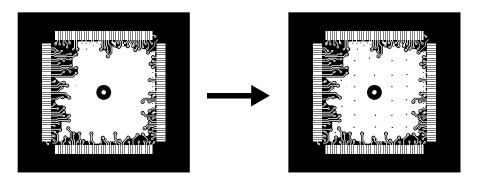

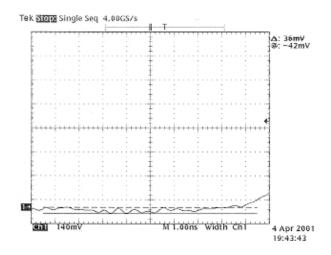

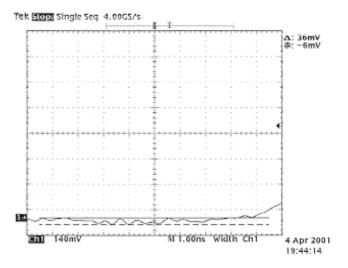

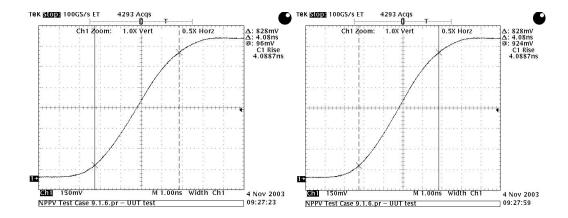

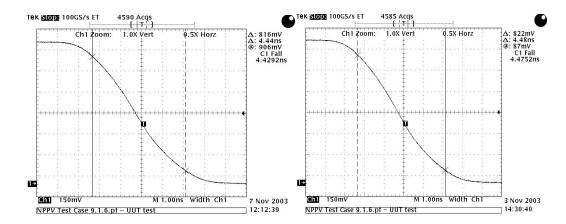

When observing waveforms on the scope display, it is important to understand the purpose of the measurement being performed. If the purpose is simply to see a complete waveform, then the horizontal and vertical scales only need to be small enough to fit the waveform on the screen and the display does not need to be set to average or infinite persistence. However, if the purpose is to obtain the most accurate measurements, more care is needed. The recommended scope settings listed

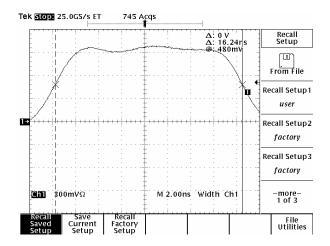

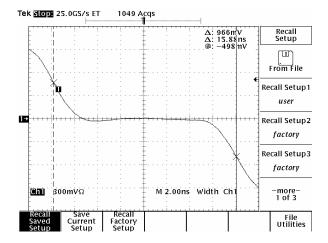

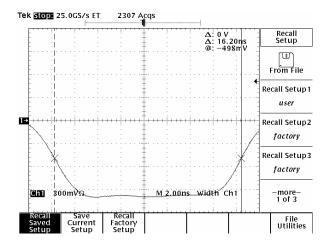

throughout the procedures should allow the desired waveform to be displayed on the screen. For the best resolution, zoom in as much as possible on the waveform as observed in the following three screen shots.

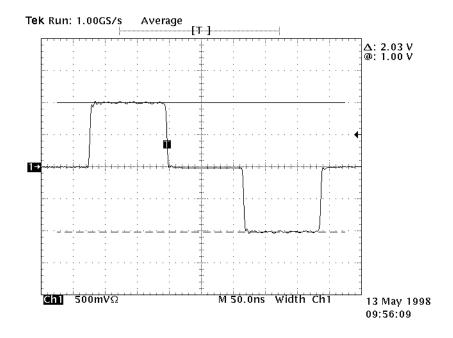

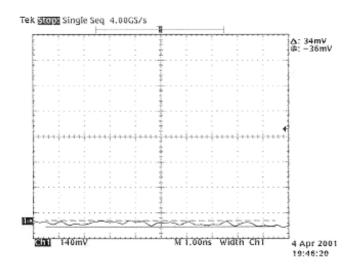

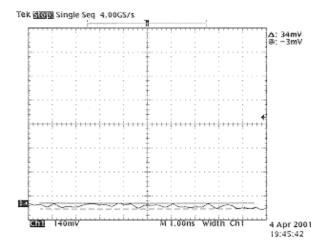

Figure 1-2. Poor Resolution (Wide View)

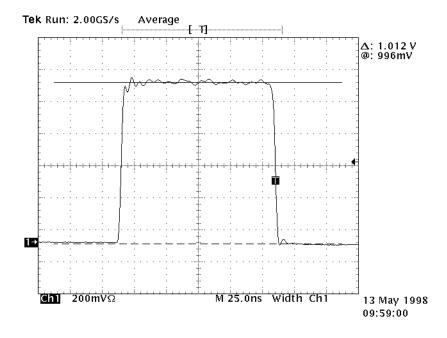

Figure 1-3. Good Resolution with Room for Improvement

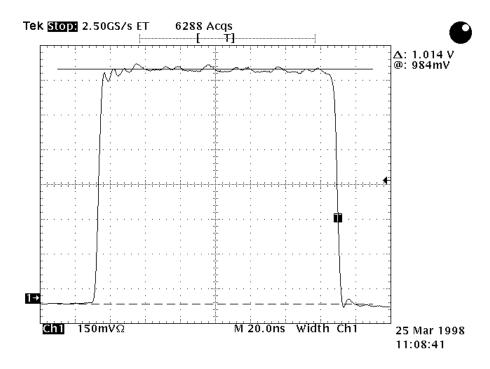

Figure 1-4. Best Resolution for Measurement

Note: The above three screen shots were not necessarily taken during the same session.

Note:

The waveform in Figure 1-4 is displayed across the entire screen, showing enough of the edge of the pulse to allow the zero point to be approximated and providing the best resolution possible for measurement.

In the example above, the "Average" setting was used on the scope to produce a sharper image. This is the best (and easiest) way to measure the amplitude, period, overshoot, and rise/fall time of a waveform. Each time a new trigger signal arrives, the scope repaints the screen with a new signal. This causes the signal to appear unstable because each successive signal is not exactly the same as the previous one. By averaging the waveforms together, random noise will be filtered from the display, and a more representative signal will appear.

Some measurements require the scope display to be set to "Infinite Persistence." In this case it is important that each successive waveform falls within specified boundary conditions. In infinite persistence mode, an adequate sample is obtained from data accumulated between a one to ten minute time period.

### 1.3 Required Test Equipment

This section describes the minimum equipment needed to complete the test.

- Digitizing oscilloscope with at least 1 GHz bandwidth (for example, Tektronix <sup>®</sup> 784).

- Two high bandwidth differential probes (for example, Tektronix P6247) with capacitance less than or equal to 1 pF and a bandwidth greater than or equal to 1 GHz. Using lower bandwidth/higher capacitance probes may cause false failures of conformance tests.

- Two computers with open PCI slots and LANConf.exe installed.

- One Intel® 82543 controller-based 1000BASE-T adapter to generate Ethernet traffic.

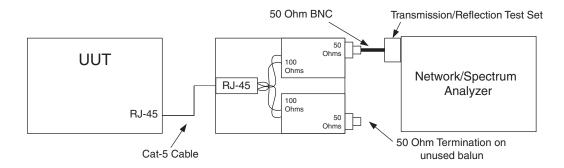

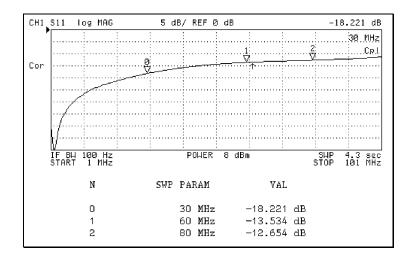

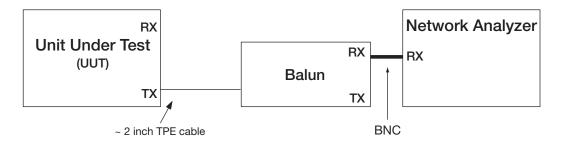

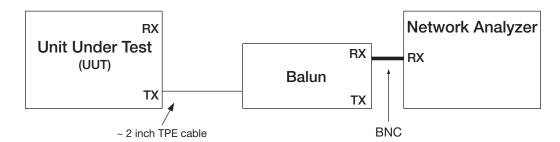

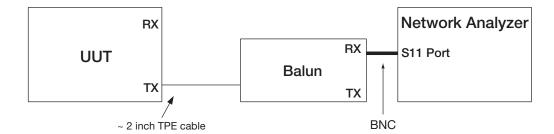

- Network/spectrum analyzer (50 KHz to 500 MHz range) with S-parameter test set.

- BNC cable with 50-ohm impedance (approximately three feet long).

- Additional test equipment may be required for 100BASE-TX and 10BASE-T testing (refer to the appropriate test procedure for a list of needed equipment).

### 1.4 Required Test Fixtures

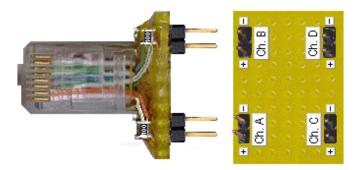

- 100  $\Omega$  load resistors—all four channels have 100 ohms (± 0.2 ohms preferred)

- Category 5 UTP cable (~2 inches long)

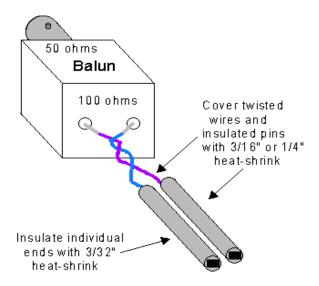

- Balun test fixture (100-ohm balanced to 50-ohm unbalanced)

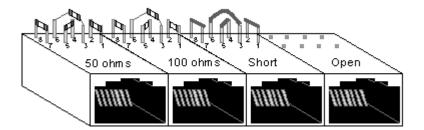

- Network analyzer calibration loads:

- · Short-circuit calibration standard

- · Open-circuit calibration standard

- · 100-ohm calibration load

- · 50-ohm calibration load

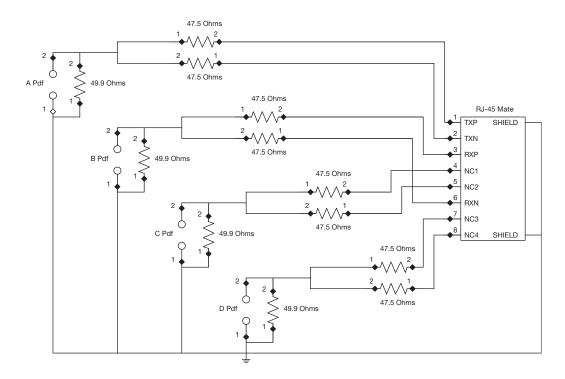

- Common-mode output voltage test fixture (IEEE 802.3, fixture 40-32)

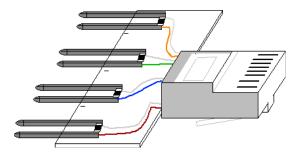

- 0.5 meter Category 5 cable, with female pins on 0.1 inch centers at one end

- Length of Category 5 cable that conforms to the following:

- For 1000BASE-T, Section 40.7 of the IEEE 802.3 specification. The parameters that have the greatest impact on cable length are insertion loss and propagation delay.

- For 100BASE-TX, Section 25.4.6 of the IEEE 802.3 specification.

- For 10BASE-T, Section 14.4 of the IEEE 802.3 specificationAlien crosstalk noise injection cable.

- · LAN adapter that can be forced into 100BASE-TX mode

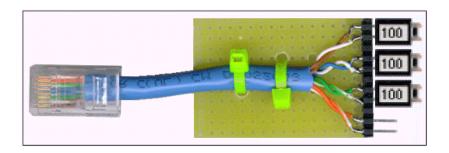

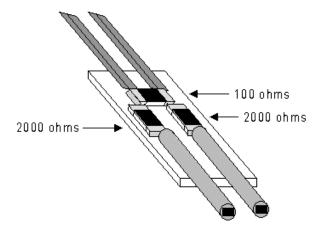

- Alien crosstalk test fixture with male and female square pins and a circuit of three resistors (two 2 KW and one 100  $\Omega)$

- Additional test fixtures are required for 100BASE-TX and 10BASE-T testing.

Appendices A through D provide test fixture illustrations and construction information.

### 1.5 Required Software and Data Patterns

Many of the tests in this procedure require the UUT to behave in a specified way. Intel's proprietary test utility, LANConf.exe, allows the UUT to be configured into the desired state and to transmit and receive specific test patterns. Contact your local Intel sales office for more details and to obtain a copy of LANConf.exe.

### 1.6 PHY Conformance Tests

There are several different ways to group the tests in this procedure, depending on the intent of the tester. The following minimum subset of tests necessary to catch the most problematic bugs in board design and implementation are listed in the three tables below.

- Pre-Test minimal initial design validation requirements. These are the first tests that should be completed.

- IEEE Compliance Test tests needed for basic IEEE testing. This test subset identifies most board design and implementation issues.

Note:

Recommended tests are for higher design and implementation confidence. These tests are not required, but if completed will ensure a higher quality design.

### **Table 1-1.**

| 1000Base-T PHY Conformance Tests                                          | Pre-<br>Test | IEEE<br>Compliance Test |

|---------------------------------------------------------------------------|--------------|-------------------------|

| 40.6.1.2.1 Peak Differential Output Voltage and Level Accuracy            | Х            | Х                       |

| 40.6.1.2.2 Maximum Output Droop                                           | Х            | Х                       |

| 40.6.1.3.2 Receiver Differential Input Signals (Receive Bit Error Rate)   | Х            | Х                       |

| 40.8.3.1 MDI Return Loss                                                  |              | Х                       |

| 40.6.1.3.4 Alien Crosstalk Noise Rejection (Differential Noise Rejection) |              | Recommended             |

| 40.8.3.3 MDI Common-Mode Output Voltage                                   |              | Recommended             |

| 100Base-TX PHY Conformance Tests             | Pre-<br>Test | IEEE<br>Compliance<br>Test |

|----------------------------------------------|--------------|----------------------------|

| 100Base-TX Differential Output Voltage (UTP) | Х            | Х                          |

| 100Base-TX Transmit Jitter                   | Х            | Х                          |

| 100Base-TX Differential Input Signals (BER)  | Х            | Х                          |

| 100Base-TX Signal Amplitude Symmetry         | Х            | Х                          |

| 100Base-TX Rise and Fall Times               | Х            | Х                          |

| 100Base-TX Duty Cycle Distortion (DCD)       | Х            | Х                          |

| 100Base-TX Receiver Return Loss              |              | X                          |

| 100Base-TX Transmitter Return Loss           |              | X                          |

| 10Base-T PHY Conformance Tests                                          | Pre-<br>Test | IEEE<br>Compliance Test |

|-------------------------------------------------------------------------|--------------|-------------------------|

| 10Base-T Peak Differential Output Voltage on TD Circuit                 | Х            | Х                       |

| 10Base-T Transmitter Output Timing Jitter without Cable Model           | Х            | Х                       |

| 10Base-T TD Circuit Impedance (Transmitter Return Loss)                 |              | Х                       |

| 10Base-T TD Circuit Common-Mode Output Voltage                          |              | Х                       |

| 10Base-T Transmitter Output Timing Jitter with Cable Model              |              | Х                       |

| 10Base-T RD Receiver Circuit Signal Acceptance Test (BER)               |              | Х                       |

| 10Base-T RD Circuit Differential Input Impedance (Receiver Return Loss) |              | Х                       |

| • 10Base-T Harmonic Content                                             |              | Recommended             |

This page is intentionally blank.

§ §

# 2 1000BASE-T Peak Differential Output Voltage and Level Accuracy

IEEE STANDARD 40.6.1.2.1

### 2.1 Test Purpose

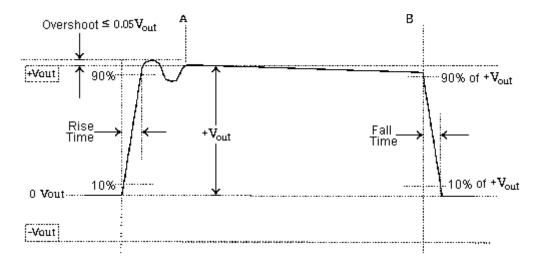

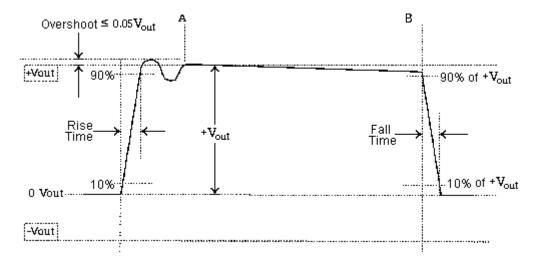

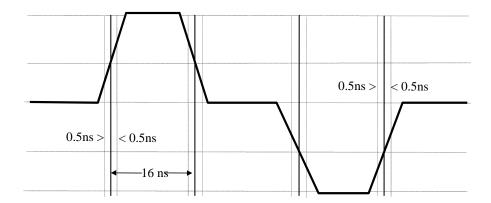

To measure the peak differential output voltage on all four channels and examine the linearity of each channel. This test uses "Test Mode 1" as defined by the IEEE 802.3 Specification, Section 40.6.1.1.2. An example of the test mode 1 waveform is shown below.

### 2.2 Specification

- Points A & B =  $\pm (0.67 \text{ to } 0.82) \text{Vpk}$

- Amplitude Symmetry: < 1% delta between A and B

- Points C & D =  $\pm (0.5*A \text{ or B}) \pm 2\%$

- The above is true for all four MDI channels.

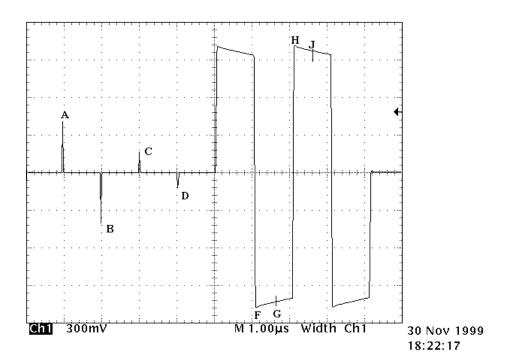

Figure 2-1. Example of Test Mode 1 Waveform

### 2.3 Test Equipment

- Digitizing oscilloscope with at least 1 GHz bandwidth

- · Differential probe with 1 GHz or greater bandwidth

1000BASE-T/100BASE-TX/10BASE-T Physical Layer Compliance Tests Manual INTEL CONFIDENTIAL 14

· UUT with LANConf.exe test software

### 2.4 Test Fixtures

• 100  $\Omega$  UTP test load (Appendix A).

### 2.5 Test Procedure

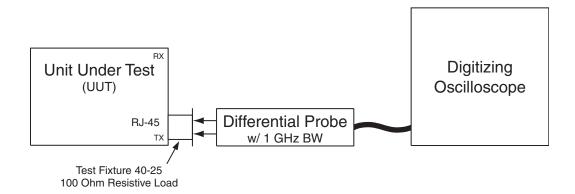

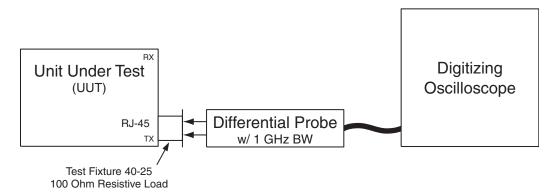

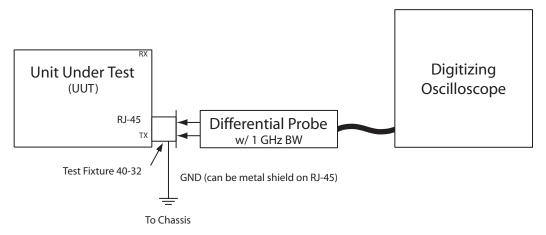

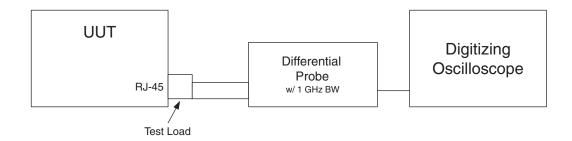

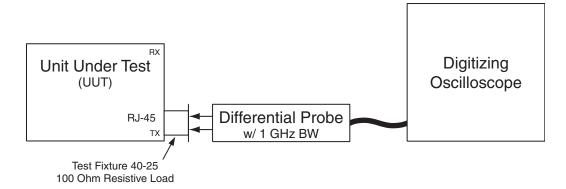

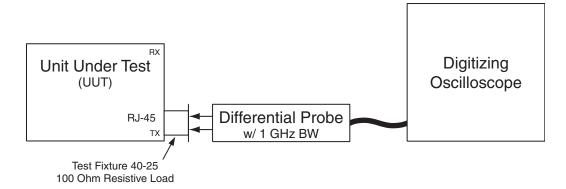

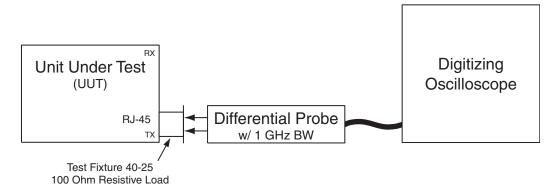

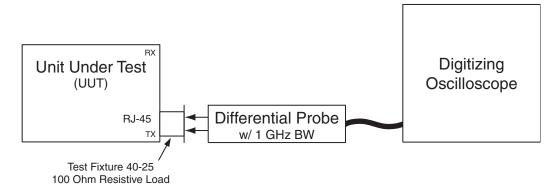

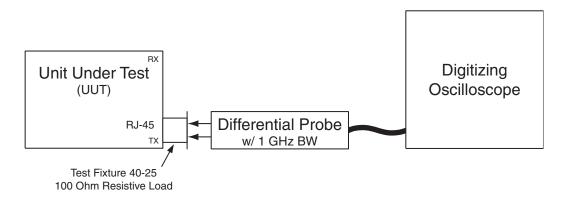

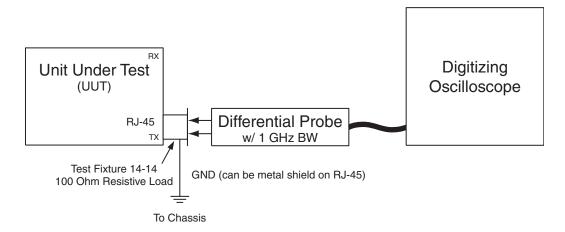

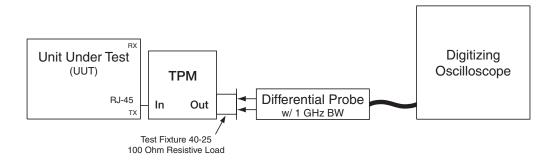

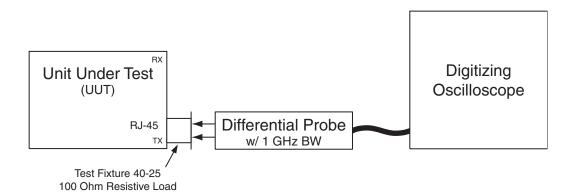

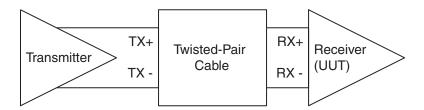

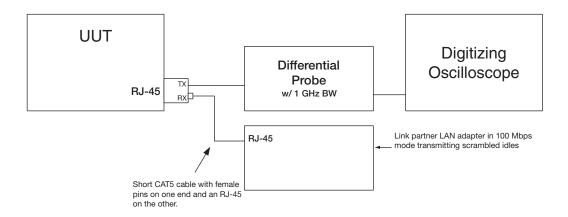

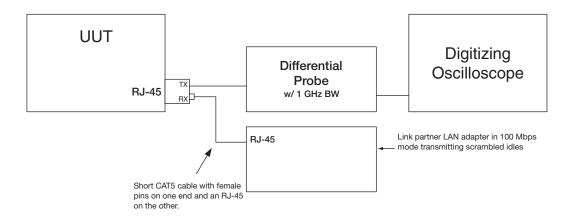

1. Connect the test equipment as shown in the figure below.

- 2. Set the probe to divide by 10 and to full bandwidth.

- 3. Select the Amplitude and Level Accuracy: 40.6.1.2.1 Test from the 1000BASE-T PHY Configuration Tests menu in LANConf.exe.

- 4. Measure the output voltage with a differential probe connected across the 100-ohm test load for each channel.

- 5. Adjust oscilloscope to the settings for Point A as shown in the following table and figure:

1000BASE-T/100BASE-TX/10BASE-T Physical Layer Compliance Tests Manual

15 INTEL CONFIDENTIAL

Table 2-1. Point A Peak Voltage

| Trigger Settings | Trigger Type      | Polarity          | Limits           | Level   |

|------------------|-------------------|-------------------|------------------|---------|

|                  | Pulse width       | Positive          | 7 ns to 9 ns     | +500 mV |

| Scaling          | Vertical Scale    | Vertical Position | Horizontal Scale |         |

|                  | 150 mV / division | -3.0 division     | 5 ns / division  |         |

| Cursors          | Display Mode      | Acquisition Mode  |                  |         |

| Horizontal bars  | Vectors           | Average on        |                  |         |

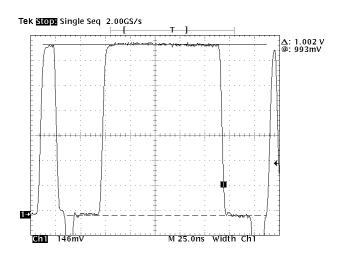

Figure 2-2. Example Point A Measurement

6. Repeat Step 5. for Point B:

Table 2-2. Point B Peak Voltage

| Trigger Settings | Trigger Type      | Polarity                  | Limits           | Level   |

|------------------|-------------------|---------------------------|------------------|---------|

|                  | Pulse width       | Negative                  | 5.6 ns to 8.6 ns | -500 mV |

| Scaling          | Vertical Scale    | Vertical Position         | Horizontal Scale |         |

|                  | 150 mV / division | +3.0 division             | 5 ns / division  |         |

| Cursors          | Display Mode      | lay Mode Acquisition Mode |                  |         |

| Horizontal bars  | Vectors           | Average on                |                  |         |

Figure 2-3. Example Point B Measurement

7. Repeat Step 5. for Point C:

June 2006 Version 4.3

Table 2-3. Point C Peak Voltage

| Trigger Settings | Trigger Type     | Polarity          | Limits           | Level  |

|------------------|------------------|-------------------|------------------|--------|

|                  | Pulse width      | Positive          | 7 ns to 9 ns     | 251 mV |

| Scaling          | Vertical Scale   | Vertical Position | Horizontal Scale |        |

|                  | 75 mV / division | -3.0 division     | 5 ns / division  |        |

| Cursors          | Display Mode     | Acquisition Mode  |                  |        |

| Horizontal bars  | Vectors          | Average on        |                  |        |

Figure 2-4. Example Point C Measurement

8. Repeat Step 5. for Point D:

Table 2-4. Point D Peak Voltage

| Trigger Settings | Trigger Type     | Polarity          | Limits           | Level   |

|------------------|------------------|-------------------|------------------|---------|

|                  | Pulse width      | Negative          | 5.6 ns to 8.6 ns | -278 mV |

| Scaling          | Vertical Scale   | Vertical Position | Horizontal Scale |         |

|                  | 75 mV / division | +3.0 division     | 5 ns / division  |         |

| Cursors          | Display Mode     | Acquisition Mode  |                  |         |

| Horizontal bars  | Vectors          | Average on        |                  |         |

Figure 2-5. Example Point D Measurement

9. Verify that the measurements meet specifications for all four points

### 3 1000BASE-T Maximum Output Droop

### IEEE STANDARD 40.6.1.2.2

### 3.1 Test Purpose

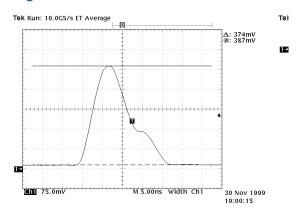

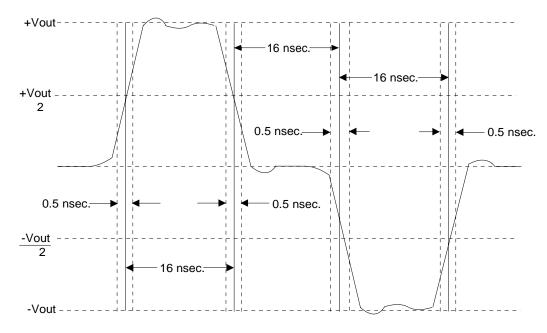

To ensure that the LAN analog front end (AFE) is capable of handling DC bias. This test uses "Test Mode 1" as defined by the IEEE 802.3 Specification, Section 40.6.1.1.2. An example of the test mode 1 waveform is shown below.

### 3.2 Specification

- Point G amplitude > 73.1% of point F amplitude; point G is exactly 500 ns after F.

- Point J amplitude > 73.1% of point H amplitude; point J is exactly 500 ns after H.

- The above is true for all four MDI channels.

If the LAN design does not meet the output droop requirement, the open circuit inductance (OCL) for all four channels of the magnetics module should be verified and equal at least 350  $\mu$ H with an 8 mA DC bias. (The OCL requirement is explained in more detail in the ANSI TP-PMD, 100BASE-TX physical layer specification.)

Figure 3-1. Example of Test Mode 1 Waveform

### 3.3 Test Equipment

- · Oscilloscope with 1GHz or greater bandwidth

- Differential probe with 1 GHz or greater bandwidth

1000BASE-T/100BASE-TX/10BASE-T Physical Layer Compliance Tests Manual INTEL CONFIDENTIAL 20

· UUT with LANConf.exe test software

#### 3.4 **Test Fixtures**

• 100  $\Omega$  UTP test load (Appendix A.1).

#### 3.5 **Test Procedure**

1. Connect the test equipment as shown in the figure below.

- 2. Set the probe to divide by 10 and to full bandwidth.

- 3. Select the Droop: 40.6.1.2.2 Test from the 1000BASE-T PHY Configuration Tests menu in LANConf.exe.

- 4. Adjust the oscilloscope to the settings for Points F and G.

Note:

When measuring points F/G or H/J for droop, trigger the oscilloscope on point B to measure points F/G and point A to measure points H/J. Use a long record length and scroll over to the points to be measured.

### **Table 3-1.**

| Point F and G: Pulse Droop                    |                   |                        |                   |         |  |

|-----------------------------------------------|-------------------|------------------------|-------------------|---------|--|

| Trigger Settings                              | Trigger Type      | pe Polarity Limits Lev |                   |         |  |

|                                               | Pulse width       | Negative               | 5.6 ns to 8.6 ns  | -500 mV |  |

| Scaling                                       | Vertical Scale    | Vertical Position      | Horizontal Scale  |         |  |

|                                               | 150 mV / division | +3.0 division          | 200 ns / division |         |  |

| Cursors                                       | Display Mode      | Acquisition Mode       |                   |         |  |

| Horizontal bars for F; Crosshairs for F and G | Vectors           | Average on             |                   |         |  |

- 5. Measure the output voltage with a differential probe connected across the 100-ohm test load for each channel.

- 6. Adjust the oscilloscope to the settings for Points H and J as shown below.

| Point H and J: Pulse Droop                          |                   |                   |                   |         |

|-----------------------------------------------------|-------------------|-------------------|-------------------|---------|

| Trigger Settings                                    | Trigger Type      | Polarity          | Polarity Limits   |         |

|                                                     | Pulse width       | Positive          | 7 ns to 9 ns      | +500 mV |

| Scaling                                             | Vertical Scale    | Vertical Position | Horizontal Scale  |         |

|                                                     | 150 mV / division | -3.0 division     | 200 ns / division | ]       |

| Cursors                                             | Display Mode      | Acquisition Mode  |                   |         |

| Horizontal bars<br>for H; Crosshairs<br>for H and J | Vectors           | Average on        |                   |         |

Note: Points F and G are like H and J, except they are negative polarity.

- 7. Measure the output voltage with a differential probe connected across the 100-ohm test load for each channel.

- 8. Compute the ratios as shown in the example below.

| Channel | Point F | Point G | Ratio   | Point H | Point J | Ratio   |

|---------|---------|---------|---------|---------|---------|---------|

| Α       | -1.024  | -0.982  | 95.898% | 1.020   | 0.984   | 96.471% |

| В       | -1.022  | -0.985  | 96.380% | 1.022   | 0.985   | 96.380% |

| С       | -1.019  | -0.985  | 96.663% | 1.018   | 0.985   | 96.853% |

| D       | -1.019  | -0.982  | 96.369% | 1.012   | 0.983   | 97.134% |

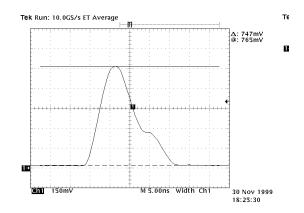

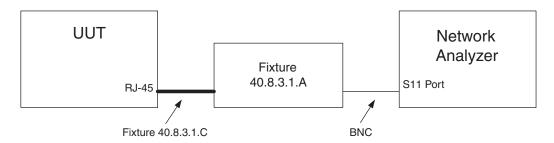

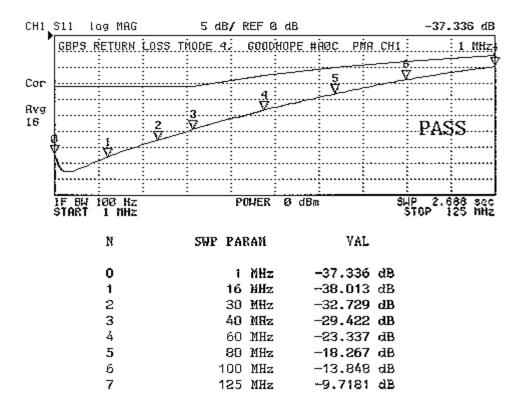

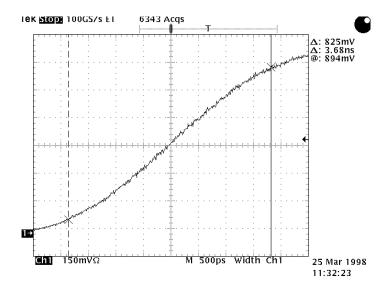

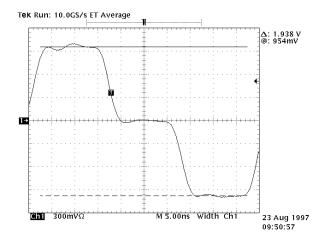

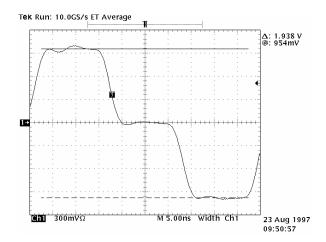

Point H peak = 1.020 Volts:

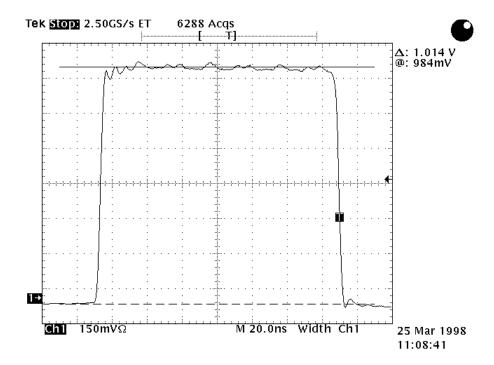

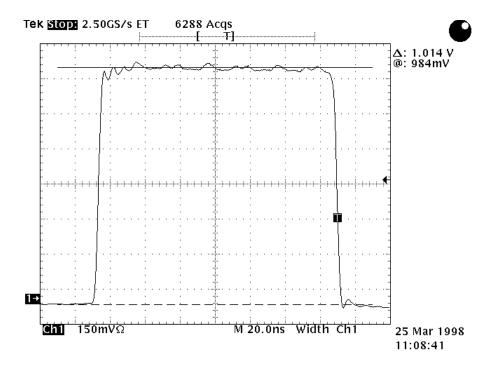

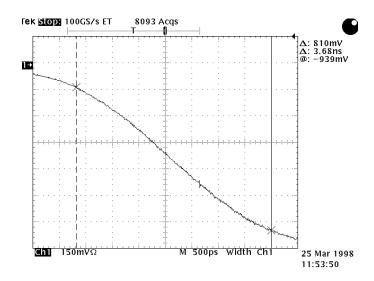

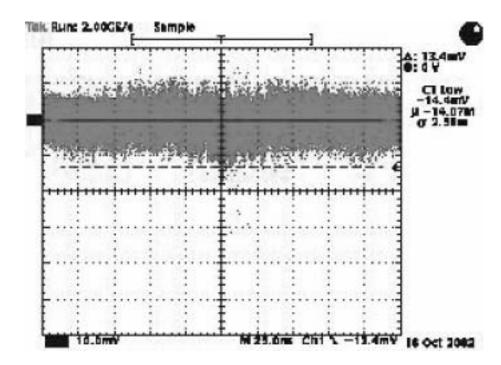

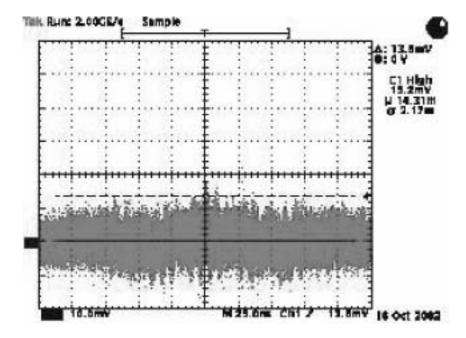

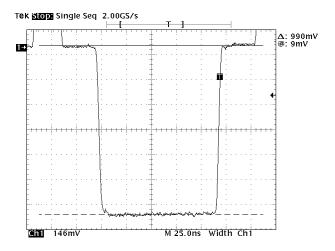

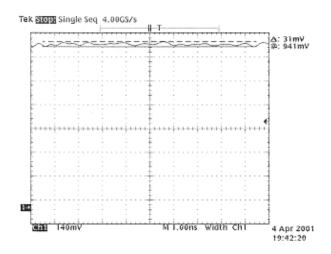

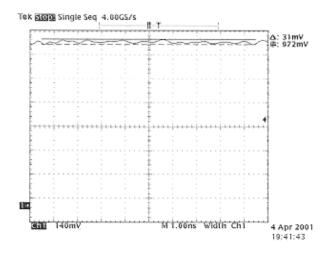

Figure 3-2. Example Maximum Output Droop Measurement, Point H

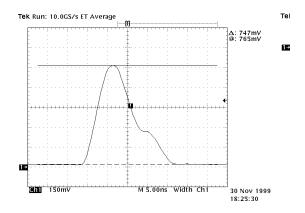

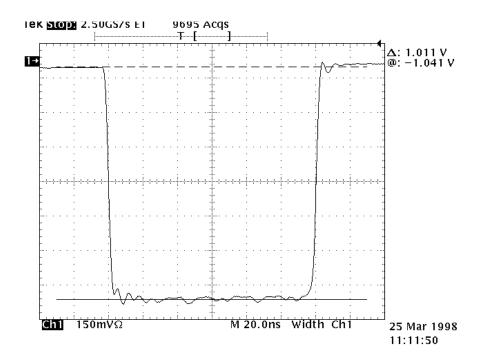

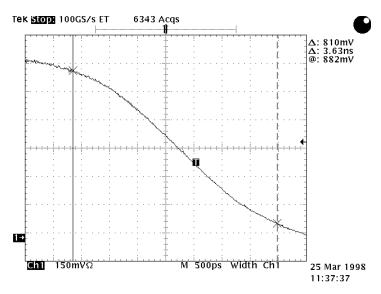

Point J, 500 ns after H = 0.984 Volts:

Figure 3-3. Example Maximum Output Droop Measurement, Point J

9. Verify the measurements meet specifications

§ §

### 4 1000BASE-T Receiver Differential Input Signals (Bit Error Rate)

IEEE STANDARD 40.6.1.3.1

#### 4.1 **Test Purpose**

To determine the UUT receiver sensitivity at various cable lengths.

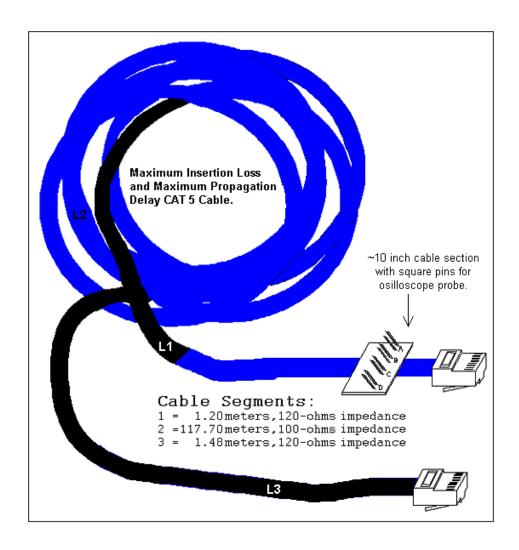

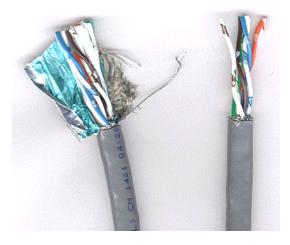

This requirement can be accomplished by performing receive bit error rate tests with specification compliant Category 5 cables across a range of lengths from approximately 1 meter to greater than 100 meters (maximum specification). Insertion loss measurements and propagation delay measurements have shown high-quality Category 5 cable ranging from 115 m to 130 m may be equal to a maximum specification cable (depending on the vendor and the cable manufacturing lot). Appendix E contains details on constructing LAN cables.

#### 4.2 **Specification**

The receiver shall have a frame error rate of less than 10<sup>7</sup> for 125 octet frames. A frame error rate of 10<sup>7</sup> for 125 octet frames is equivalent to a bit error rate (BER) of 10<sup>10</sup> for any size of frame.

#### 4.3 **Test Equipment**

- · UUT with LANConf.exe software

- Second system running LANConf.exe with either a 1000BASE-T network interface card (NIC) or LAN on Motherboard (LOM) for the link partner

- Various lengths of Category 5 cable between 1 and 100 meters One of the cable lengths should be equivalent to the maximum cable length described in the IEEE 802.3 standard, Section 40.7.

#### 4.4 **Test Fixtures**

Various lengths of Category 5 cable between 1 and 100 meters (Appendix A).

#### 4.5 **Test Procedure**

- 1. Connect the UUT and the link partner using the desired Category 5 cable length and verify that a gigabit link has been established.

- 2. On the receiving system, go to the Transmit and Receive menu, and select the Receive option.

- 3. On the UUT, go to the Transmit and Receive menu, and select the Transmit option.

- 4. Allow the proper number of frames to be sent (see Section 4.6).

- 5. After transmissions is complete, press the <Esc> key on the receiver first and then the transmitter to stop the test and record the following results:

- Link partner: Transmit Good Packets and Transmit Total Packets. Both of these statistics should equal each other.

- b. UUT: Receive Good Packets and Missed Packets.

- 6. Calculate the bit error rate (BER).

June 2006 INTEL CONFIDENTIAL Version 4.3 24

- 7. Repeat steps 1 through 7 for each cable length.

- 8. Verify the measurements meet specifications

### 4.6 Calculating Bit Error Rate (BER)

The basic BER equation is as follows:

$$BER = \frac{TGP - MP - RGP}{TGP \times BF \times BB}$$

where:

- TGP = number of good frames transmitted (#\_Transmit\_Good\_Packets)

- MP = number of missed packets (#\_Missed\_Packets)

- RGP = number of good frames received (#\_Receive\_Good\_Packets)

- BF = number of bytes/frame

- BB = 8 (number of bits/byte)

Note:

Conditions where the transmit link partner overwhelms the receive unit should be avoided. When this happens, the receive statistics counters may show "RX No Resources", "RX No Buffers", or a large number of missed packets. This complicates the BER calculation and the equations for the calculations will not yield accurate BER numbers. The TX transmit speed (frames per second) can be decreased to prevent this condition. Alternatively, the test operator can try to make sure the receive unit is always in a faster PC than the transmit unit.

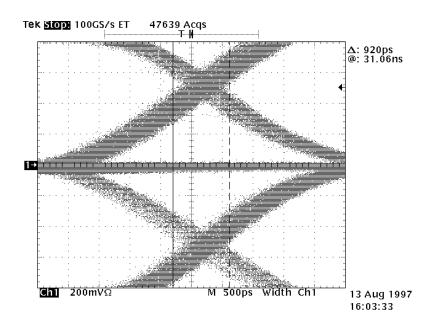

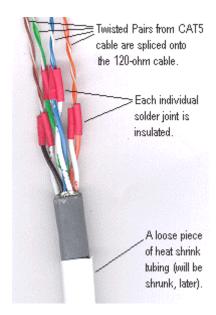

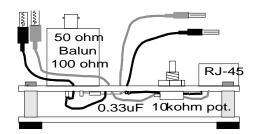

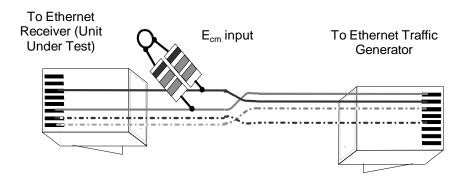

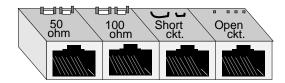

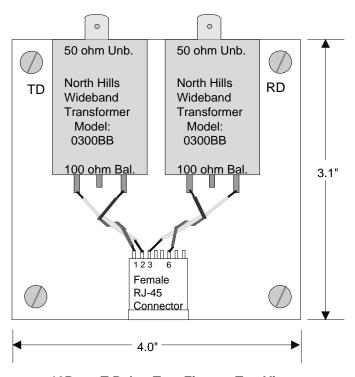

### **Example 4-1 BER Calculation Example**