# 25G Ethernet Intel<sup>®</sup> Stratix<sup>®</sup> 10 FPGA IP Design Example User Guide

Updated for Intel<sup>®</sup> Quartus<sup>®</sup> Prime Design Suite: **19.2**

IP Version: 19.2.0

ID: 683252 Version: 2020.06.18

UG-20110

## Contents

| 1. 25G Ethernet Intel <sup>®</sup> FPGA IP Quick Start Guide                                                   | 4  |

|----------------------------------------------------------------------------------------------------------------|----|

| 1.1. Directory Structure                                                                                       | 5  |

| 1.2. Generating the Design Example                                                                             | 6  |

| 1.2.1. Design Example Parameters                                                                               |    |

| 1.3. Simulating the 25G Ethernet Intel FPGA IP Design Example Testbench<br>1.3.1. Procedure                    |    |

| 1.4. Compiling and Configuring the Design Example in Hardware                                                  |    |

| 1.4.1. Procedure                                                                                               | 8  |

| 1.5. Changing Target Device in Hardware Design Example                                                         |    |

| 1.5.1. Procedure                                                                                               |    |

| 1.6. Testing the 25G Ethernet Intel FPGA IP Design in Hardware                                                 |    |

| 1.6.1. Procedure                                                                                               | 10 |

| 2. 10G/25G Ethernet Single-Channel Design Example for Intel Stratix 10 Devices                                 |    |

| 2.1. Features                                                                                                  |    |

| 2.2. Hardware and Software Requirements                                                                        |    |

| 2.3. Functional Description                                                                                    |    |

| 2.3.1. Design Components                                                                                       |    |

| 2.4. Simulation                                                                                                |    |

| 2.4.1. Testbench                                                                                               |    |

| 2.4.2. Simulation Design Example Components<br>2.4.3. Test Case—Design Example Without the IEEE 1588v2 Feature |    |

| 2.4.4. Test Case—Design Example without the IEEE 1588v2 Feature                                                |    |

| 2.5. Compilation                                                                                               |    |

| 2.6. Hardware Testing                                                                                          |    |

| 2.6.1. Test Procedure—Design Example Without the IEEE 1588v2 Feature                                           |    |

| 2.6.2. Test Procedure—Design Example with the IEEE 1588v2 Feature                                              |    |

| 3. 25G Ethernet Single-Channel Design Example for Intel Stratix 10 Devices                                     | 27 |

| 3.1. Features                                                                                                  |    |

| 3.2. Hardware and Software Requirements                                                                        |    |

| 3.3. Functional Description                                                                                    |    |

| 3.3.1. Design Components                                                                                       |    |

| 3.4. Simulation                                                                                                |    |

| 3.4.1. Testbench                                                                                               |    |

| 3.4.2. Simulation Design Example Components                                                                    |    |

| 3.4.3. Test Case—Design Example Without the IEEE 1588v2 Feature                                                |    |

| 3.4.4. Test Case—Design Example with the IEEE 1588v2 Feature<br>3.5. Compilation                               |    |

| 3.6. Hardware Testing                                                                                          |    |

| 3.6.1. Test Procedure—Design Example With and Without the IEEE 1588v2 Feature.                                 |    |

| 4. 25G Ethernet Multi-Channel Design Example for Intel Stratix 10 Devices                                      | 38 |

| 4.1. Features                                                                                                  |    |

| 4.2. Hardware and Software Requirements                                                                        |    |

| 4.3. Functional Description                                                                                    |    |

| 4.3.1. Design Components                                                                                       | 39 |

| 4.4. Simulation                                                                                                |    |

| 4.4.1. Testbench                                                                                        | 40   |

|---------------------------------------------------------------------------------------------------------|------|

| 4.4.2. Simulation Design Example Components                                                             | 41   |

| 4.4.3. Test Case                                                                                        | 41   |

| 4.5. Compilation                                                                                        | 44   |

| 4.6. Hardware Testing                                                                                   |      |

| 4.6.1. Test Procedure                                                                                   |      |

| 5. 25G Ethernet Intel FPGA IP Design Example References                                                 | . 46 |

| 5.1. Design Example Interface Signals                                                                   | 46   |

| 5.2. Design Example Registers                                                                           |      |

| 5.3. Using Transceiver Toolkit on H-Tile Production Device                                              |      |

| 6. 25G Ethernet Intel Stratix 10 FPGA IP Design Example User Guide Archives                             | . 50 |

| 7. Document Revision History for the 25G Ethernet Intel Stratix 10 FPGA IP Design<br>Example User Guide | 51   |

|                                                                                                         |      |

## **1. 25G Ethernet Intel<sup>®</sup> FPGA IP Quick Start Guide**

The 25G Ethernet (25GbE) Intel<sup>®</sup> FPGA IP core for Intel Stratix<sup>®</sup> 10 devices provides the capability of generating design examples for selected configurations.

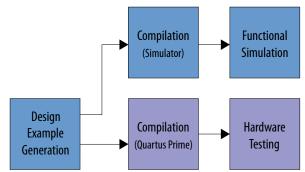

## Figure 1. Development Stages for the Design Example

### **Related Information**

10G/25G Ethernet Single-Channel Design Example for Intel Stratix 10 Devices on page 12

Provides details for the 10G/25G Ethernet single-channel design example.

25G Ethernet Single-Channel Design Example for Intel Stratix 10 Devices on page 27

Provides details for the 25G Ethernet single-channel design example.

25G Ethernet Multi-Channel Design Example for Intel Stratix 10 Devices on page 38

Provides details for the 25G Ethernet multi-channel design example.

• 25G Ethernet Intel FPGA IP Release Note Provides information about the new features and updates for each IP release.

## **1.1. Directory Structure**

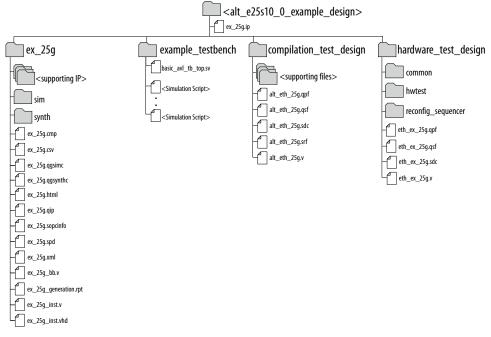

## Figure 2. Directory Structure for the 25G and 10G/25G Ethernet Design Examples

- The simulation files (testbench for simulation only) are located in <design\_example\_dir>/example\_testbench.

- The compilation-only design example is located in <design\_example\_dir>/ compilation\_test\_design.

- The hardware configuration and test files (the design example in hardware) are located in <design\_example\_dir>/hardware\_test\_design.

### Table 1. Directory and File Descriptions

| File Names      | Description                                                                                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------|

| eth_ex_25g.qpf  | Intel Quartus <sup>®</sup> Prime project file.                                                                    |

| eth_ex_25g.qsf  | Intel Quartus Prime project settings file.                                                                        |

| eth_ex_25g.sdc  | Synopsys Design Constraints file. You can copy and modify this file for your own 25GbE Intel FPGA IP core design. |

| eth_ex_25g.v    | Top-level Verilog HDL design example file.<br>Single-channel design uses Verilog file.                            |

| common/         | Hardware design example support files.                                                                            |

| hwtest/main.tcl | Main file for accessing System Console.                                                                           |

## **1.2. Generating the Design Example**

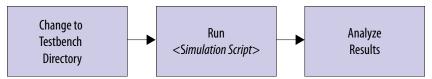

## Figure 3. Procedure

## Figure 4. Example Design Tab in the 25G Ethernet Intel FPGA IP Parameter Editor

| em:my_25g Pa        | th: alt_e25s10_0                                                                                                                        |                         |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                     | ntel FPGA IP                                                                                                                            | Details                 |

| 25s10               |                                                                                                                                         | Generate Example Design |

| Example Desig       | jn l                                                                                                                                    |                         |

| Available Exampl    | e Designs                                                                                                                               |                         |

| xample design:      | Single-Channel Design 💌                                                                                                                 |                         |

| Example Design      | Files                                                                                                                                   |                         |

| Simulation          |                                                                                                                                         |                         |

| Synthesis           |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

| enerated HDL F      |                                                                                                                                         |                         |

| enerate File Form   | at: Verilog 📼                                                                                                                           |                         |

|                     |                                                                                                                                         |                         |

| Target Developm     |                                                                                                                                         |                         |

| elect board:        | Stratix 10 GX Signal Integrity L-Tile (Prod) Development Kit 💌                                                                          |                         |

| arget device: 15X   | 280LU2F50E1YG                                                                                                                           |                         |

| -                   |                                                                                                                                         |                         |

| elected design su   | pports generation, simulation, and Quartus compile flows for any<br>he hardware support is provided through selected Development kit(s) |                         |

| ith a specific devi | ce. To exclude hardware aspects of example design, select "None"                                                                        |                         |

| om the "Target D    | evelopment Kit* pull down menu.                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

|                     |                                                                                                                                         |                         |

Follow these steps to generate the hardware design example and testbench:

- In the Intel Quartus Prime Pro Edition software, click File ➤ New Project Wizard to create a new Quartus Prime project, or File ➤ Open Project to open an existing Quartus Prime project. The wizard prompts you to specify a device.

- 2. In the IP Catalog, locate and select **25G Ethernet Intel FPGA IP**. The **New IP Variation** window appears.

- 3. Specify a top-level name for your IP variation and click OK. The parameter editor adds the top-level .ip file to the current project automatically. If you are prompted to manually add the .ip file to the project, click Project ➤ Add/ Remove Files in Project to add the file.

- In the Intel Quartus Prime Pro Edition software, you must select a specific Intel Stratix 10 device in the **Device** field, or keep the default device that the Intel Quartus Prime software proposes.

- *Note:* The hardware design example overwrites the selection with the device on the target board. You specify the target board from the menu of design example options in the **Example Design** tab (Step 8).

- 5. Click **OK**. The parameter editor appears.

- 6. On the **IP** tab, specify the parameters for your IP core variation.

- 7. On the **Example Design** tab, for **Example Design Files**, select the **Simulation** option to generate the testbench, and select the **Synthesis** option to generate the hardware design example. Only Verilog HDL files are generated.

*Note:* A functional VHDL IP core is not available. Specify Verilog HDL only, for your IP core design example.

- 8. For Target Development Kit, select the Stratix 10 GX Signal Integrity L-Tile (Prod) Development Kit.

- *Note:* The target device of the generated hardware example design is for Intel Stratix 10 GX Signal Integrity L-Tile (Production) Development Kit (1SX280LU2F50E1VG) and may differ from your selected device. The target device can be changed after hardware design example generation has completed. For the procedure to change the target device, refer to *Changing Target Device in Hardware Design Example*.

- 9. Click **Generate Example Design**. The **Select Example Design Directory** window appears.

- 10. If you want to modify the design example directory path or name from the defaults displayed (alt\_e25s10\_0\_example\_design), browse to the new path and type the new design example directory name (<design\_example\_dir>).

- 11. Click OK.

## **Related Information**

Changing Target Device in Hardware Design Example on page 9

## **1.2.1. Design Example Parameters**

## Table 2.Parameters in the Example Design Tab

| Parameter            | Description                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Example Design       | Available example designs for the IP parameter settings.                                                                                                                                                                                                                                                                                                             |  |

| Example Design Files | <ul> <li>The files to generate for the different development phase.</li> <li>Simulation—generates the necessary files for simulating the example design.</li> <li>Synthesis—generates the synthesis files. Use these files to compile the design in the Intel Quartus Prime Pro Edition software for hardware testing and perform static timing analysis.</li> </ul> |  |

| Generate File Format | The format of the RTL files for simulation—Verilog.                                                                                                                                                                                                                                                                                                                  |  |

| Select Board         | Supported hardware for design implementation. When you select an Intel FPGA development board, use device 1SX280LU2F50E1VG as the <i>Target Device</i> for design example generation. If this menu is not available, there is no supported board for the options that you select.                                                                                    |  |

|                      | Stratix 10 GX Signal Integrity L-Tile (Prod) Development Kit: This option allows you to test the design example on the selected Intel FPGA IP development kit. This option automatically selects the <i>Target Device</i> of 1SX280LU2F50E1VG. If your board revision has a different device grade, you can change the target device.                                |  |

|                      | <b>None</b> : This option excludes the hardware aspects for the design example.                                                                                                                                                                                                                                                                                      |  |

# **1.3. Simulating the 25G Ethernet Intel FPGA IP Design Example Testbench**

## 1.3.1. Procedure

You can compile and simulate the design by running a simulation script from the command prompt.

- At the command prompt, change the working directory to <design\_example\_dir>/example\_testbench.

- 2. Run the simulation script for the supported simulator of your choice. The script compiles and runs the testbench in the simulator.

## Table 3. Steps to Simulate the Testbench

| Simulator | Instructions                                                                                                                                                  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ModelSim* | In the command line, type vsim -do run_vsim.do.                                                                                                               |  |

|           | If you prefer to simulate without bringing up the ModelSim GUI, type vsim -c -do run_vsim.do.                                                                 |  |

|           | <i>Note:</i> The ModelSim-AE and ModelSim-ASE simulators cannot simulate this IP core. You must use another supported ModelSim simulator such as ModelSim SE. |  |

| VCS*      | In the command line, type sh run_vcs.sh                                                                                                                       |  |

| NCSim     | In the command line, type sh run_ncsim.sh                                                                                                                     |  |

| Xcelium*  | In the command line, type sh run_xcelium.sh                                                                                                                   |  |

### A successful simulation ends with the following message:

Simulation Passed. or Testbench complete. After successful completion, you can analyze the results.

## **1.4. Compiling and Configuring the Design Example in Hardware**

The 25G Ethernet Intel FPGA IP core parameter editor allows you to compile and configure the design example on a target development kit.

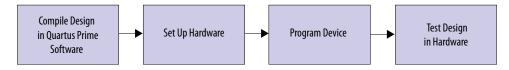

## 1.4.1. Procedure

To compile and configure a design example on hardware, follow these steps:

- 1. Launch the Intel Quartus Prime Pro Edition software and select **Processing** ➤ **Start Compilation** to compile the design.

- 2. After you generate an SRAM object file .sof, follow these steps to program the hardware design example on the Intel Stratix 10 device:

- a. On the Tools menu, click Programmer.

- b. In the Programmer, click **Hardware Setup**.

- c. Select a programming device.

- d. Select and add the Intel Stratix 10 GX board to your Intel Quartus Prime Pro Edition session.

- e. Ensure that Mode is set to JTAG.

- f. Select the Intel Stratix 10 device and click Add Device. The Programmer displays a block diagram of the connections between the devices on your board.

- g. In the row with your .sof, check the box for the .sof.

- h. Check the box in the **Program/Configure** column.

- i. Click Start.

- *Note:* This design targets the Intel Stratix 10 device. Please contact your Intel FPGA representative to inquire about a platform suitable to run this hardware example.

## **Related Information**

- Incremental Compilation for Hierarchical and Team-Based Design

- Programming Intel FPGA Devices

## **1.5. Changing Target Device in Hardware Design Example**

If you have selected **Intel Stratix 10 GX Signal Integrity L-Tile (Production) Development Kit** as your target device, the 25G Ethernet Intel FPGA IP core generates a hardware example design for target device 1SX280LU2F50E1VG. This device may differ from the device on your development kit.

## 1.5.1. Procedure

To change the target device in your hardware design example, follow these steps:

- 1. Launch the Intel Quartus Prime Pro Edition software and open the hardware test project file /hardware\_test\_design/eth\_ex\_25g.qpf.

- 2. On the **Assignments** menu, click **Device**. The **Device** dialog box appears.

- 3. In the **Device** dialog box, select 1SG280LU2F50E2VG (L-tile) or 1SG280HU1F50E2VG (H-tile) in the target device table that matches the device part number on your development kit. Refer to the *Stratix 10 GX Signal Integrity Development Kit* link on the Intel website for more information.

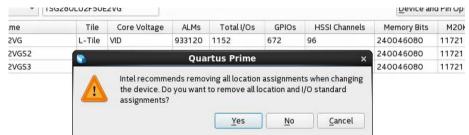

- 4. A prompt appears when you select a device, as shown in the figure below. Select **No** to preserve the generated pin assignments and I/O assignments.

## Figure 5. Intel Quartus Prime Prompt for Device Selection

If you select 1SG280HU2F50E2VG (H-Tile GX) as your target device, click Upgrade IP Components in the Project menu, select 25G Ethernet FPGA IP from the list of IP components, and click Upgrade in Editor. Regenerate this IP component.

*Note:* If you select 1SG280LU1F50E2VG (L-Tile GX) as your target device, skip this step if you are using the same Quartus and IP version.

- 6. Modify the pin assignment of cpu\_resetn port to pin AW10 through Pin Planner or Assignment Editor in the Intel Quartus Prime Pro Edition. No other pin assignment modifications are required for the design example. When you generate the design example targeting other Intel Stratix 10 development kits, refer to the respective development kit user guides for pin assignment.

- 7. Perform full compilation of your design.

You can now test the design on your hardware.

## **Related Information**

- Stratix 10 GX Signal Integrity Development Kit

- Intel Stratix 10 GX Transceiver Signal Integrity Development Kit User Guide

## **1.6. Testing the 25G Ethernet Intel FPGA IP Design in Hardware**

## **1.6.1. Procedure**

After you compile the 25G Ethernet Intel FPGA IP core design example and configure it on your Intel Stratix 10 device, you can use the System Console to program the IP core and its embedded Native PHY IP core registers.

To turn on the System Console and test the hardware design example, follow these steps:

- In the Intel Quartus Prime Pro Edition software, select Tools ➤ System Debugging Tools ➤ System Console to launch the system console.

- In the Tcl Console pane, type cd hwtest to change directory to / hardware\_test\_design/hwtest.

- 3. Type source main.tcl to open a connection to the JTAG master.

Follow the test procedure in the *Hardware Testing* section of the design example and observe the test results in the System Console.

1. 25G Ethernet Intel<sup>®</sup> FPGA IP Quick Start Guide 683252 | 2020.06.18

## **Related Information**

Analyzing and Debugging Designs with System Console

## **2. 10G/25G Ethernet Single-Channel Design Example for Intel Stratix 10 Devices**

The 10G/25G Ethernet single-channel design example demonstrates an Ethernet solution for Intel Stratix 10 devices using the 25G Ethernet Intel FPGA IP core.

Generate the design example from the **Example Design** tab of the 25G Ethernet Intel FPGA IP parameter editor. You can choose to generate the design with or without the IEEE 1588v2 feature. You can also choose to generate the design with or without the Reed-Solomon Forward Error Correction (RS-FEC) feature.

## **2.1. Features**

- Supports single Ethernet channel operating at either 10G or 25G.

- Generate design example with IEEE 1588v2 feature.

- Generate design example with RS-FEC feature.

- Generates design example separately from Intel Stratix 10 Transceiver Native PHY.

- Provides testbench and simulation script.

## 2.2. Hardware and Software Requirements

Intel uses the following hardware and software to test the design example in a Linux system:

- Intel Quartus Prime Pro Edition software.

- ModelSim-SE, NCSim (Verilog only), VCS, and Xcelium simulator.

- Intel Stratix 10 GX Signal Integrity L-Tile (Production) Development Kit (1SX280LU2F50E1VG) for hardware testing.

## **2.3. Functional Description**

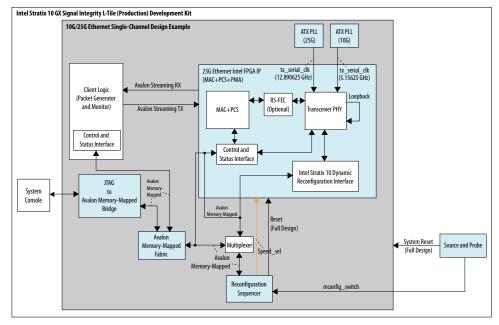

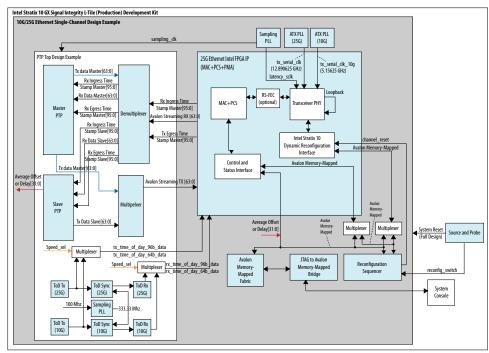

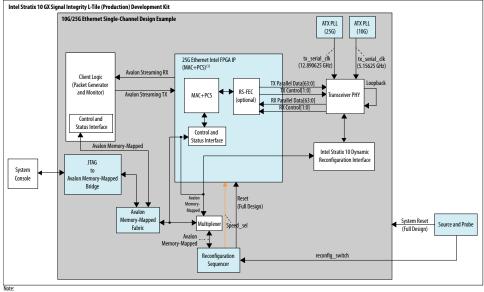

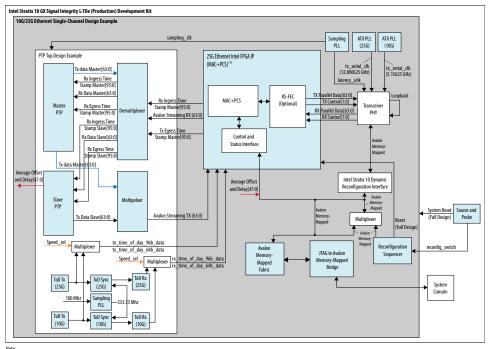

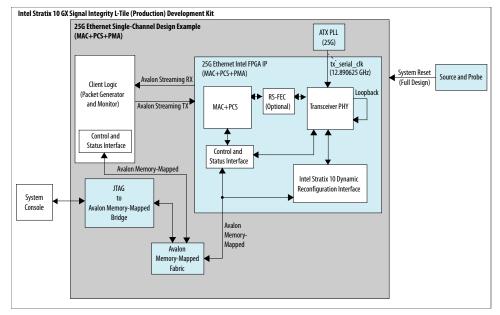

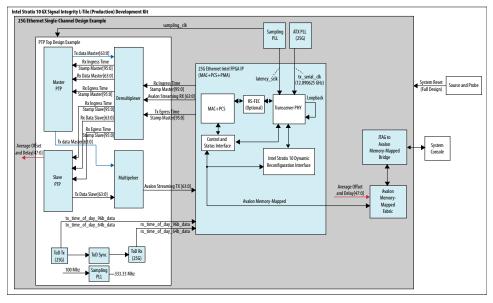

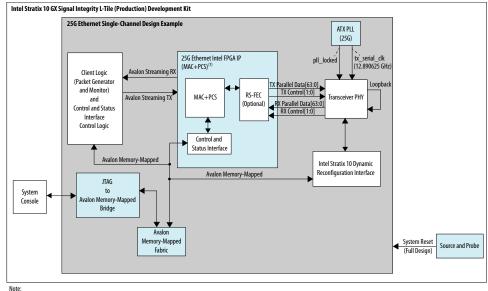

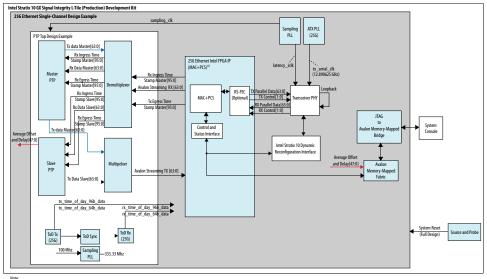

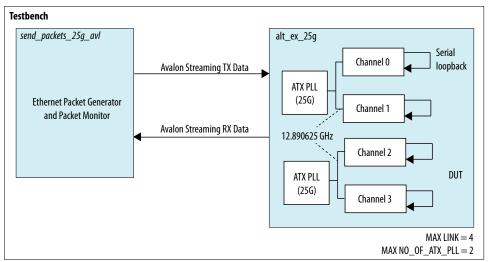

The 10G/25G Ethernet single-channel design example consists of two core variants— MAC+PCS+PMA and MAC+PCS. The following block diagrams show the design components and the top-level signals of the two core variants in the 10G/25G Ethernet single-channel design example.

## Figure 6. Block Diagram—10G/25G Ethernet Single-Channel Design Example (MAC +PCS+PMA Core Variant) Without the IEEE 1588v2 Feature

## Figure 7. Block Diagram—10G/25G Ethernet Single-Channel Design Example (MAC +PCS+PMA Core Variant) with the IEEE 1588v2 Feature

## Figure 8.Block Diagram-10G/25G Ethernet Single-Channel Design Example (MAC<br/>+PCS Core Variant) Without the IEEE 1588v2 Feature

1. Components outside of this block are part of the design example only.

## Figure 9. Block Diagram—10G/25G Ethernet Single-Channel Design Example (MAC +PCS Core Variant) with the IEEE 1588v2 Feature

Note: 1. Components outside of this block are part of the design example only.

## **2.3.1. Design Components**

## Table 4.Design Components

| Component                               | Description                                                                                                                                                                                 |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 25G Ethernet Intel FPGA IP              | Consists of MAC, PCS, and Transceiver PHY, with the following configuration:                                                                                                                |  |

|                                         | Core Variant: MAC+PCS+PMA, MAC+PCS                                                                                                                                                          |  |

|                                         | Enable flow control: Optional                                                                                                                                                               |  |

|                                         | Enable link fault generation: Optional                                                                                                                                                      |  |

|                                         | Enable preamble passthrough: Optional                                                                                                                                                       |  |

|                                         | Enable statistics collection: Optional                                                                                                                                                      |  |

|                                         | Enable MAC statistics counters: Optional                                                                                                                                                    |  |

|                                         | Enable 10G/25G dynamic rate switching: Selected                                                                                                                                             |  |

|                                         | Enable Native PHY Debug Master Endpoint (NPDME): Optional                                                                                                                                   |  |

|                                         | • Reference clock frequency: 644.531250/322.265625                                                                                                                                          |  |

|                                         | For the design example with the IEEE 1588 feature, the following additional parameters are configured:                                                                                      |  |

|                                         | Enable IEEE 1588: Selected                                                                                                                                                                  |  |

|                                         | • <b>Time of day format</b> : Enable 96-bit timestamp format <sup>(1)</sup>                                                                                                                 |  |

|                                         | For the design example with the RS-FEC feature, the following additional parameter is                                                                                                       |  |

|                                         | configured: <ul> <li>Enable RS-FEC: Selected</li> </ul>                                                                                                                                     |  |

|                                         | • Eliable RS-FEC. Selected                                                                                                                                                                  |  |

| Reconfiguration Sequencer               | Reconfigures the transceiver channel speed from 10 Gbps to 25 Gbps, and vice versa.                                                                                                         |  |

| ATX PLL                                 | Generates TX serial clocks for the 10G and 25G transceivers.                                                                                                                                |  |

| Client logic                            | Consists of:                                                                                                                                                                                |  |

|                                         | • Traffic generator, which generates burst packets to the 25G Ethernet Intel FPGA IP core                                                                                                   |  |

|                                         | for transmission.                                                                                                                                                                           |  |

|                                         | • Traffic monitor, which receives burst packets from the 25G Ethernet Intel FPGA IP core.                                                                                                   |  |

| Source and Probe                        | Source and probe signals, including system reset input signal, which you can use for debugging.                                                                                             |  |

| Design Components for th                | e IEEE 1588v2 Feature                                                                                                                                                                       |  |

| Sampling PLL                            | Generates the clocks for the IEEE 1588v2 design components.                                                                                                                                 |  |

| . 5                                     | • latency sclk: 156.25 MHz for latency measurement.                                                                                                                                         |  |

|                                         | <ul> <li>sampling_clk: 250 MHz for ToD synchronization</li> </ul>                                                                                                                           |  |

| Time-of-day (ToD) Sync                  | Synchronizes the 10G and 25G ToDs.                                                                                                                                                          |  |

| ToD Tx                                  | ToD for transmit paths for the 10G and 25G transceivers.                                                                                                                                    |  |

|                                         | ToD for receive paths for the 10G and 25G transceivers.                                                                                                                                     |  |

|                                         |                                                                                                                                                                                             |  |

| Master Precision Time<br>Protocol (PTP) | Master PTP consists of a packet generator and a packet receiver.                                                                                                                            |  |

|                                         | Packet generator: Obtains timestamp information from the 25G Ethernet Intel FPGA IP core and generates Avalon <sup>®</sup> streaming packets such as Sync packet and Delay Response packet. |  |

|                                         | • Packet receiver: Obtains the delay request packet information from the 25G Ethernet Intel FPGA IP core and produces timestamp values.                                                     |  |

| Slave PTP                               | Slave PTP consists of a packet generator, a packet receiver, and packet compute.                                                                                                            |  |

|                                         | continued                                                                                                                                                                                   |  |

<sup>&</sup>lt;sup>(1)</sup> The 10G/25G Ethernet single-channel design example with IEEE 1588v2 feature only supports 96-bit timestamp format.

| Component | Description                                                                                                                                                     |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | • Packet generator: Obtains timestamp information from the 25G Ethernet Intel FPGA IP core and generates Avalon streaming packets such as Delay Request packet. |  |

|           | • Packet receiver: Obtains the Sync and Delay Response packets information from the 25G Ethernet Intel FPGA IP core and produces timestamp values.              |  |

|           | <ul> <li>Packet compute: Calculates and produces the delay and offsets value based on the<br/>timestamp values.</li> </ul>                                      |  |

## 2.4. Simulation

The testbench sends traffic through the IP core, exercising the transmit side and receive side of the IP core.

## **Related Information**

Simulating the 25G Ethernet Intel FPGA IP Design Example Testbench on page 8

## 2.4.1. Testbench

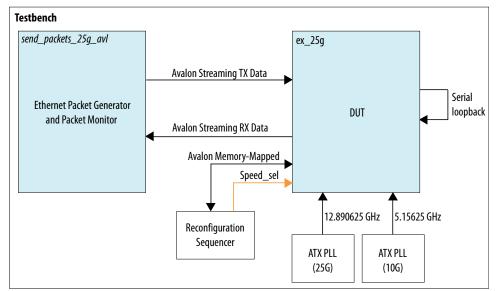

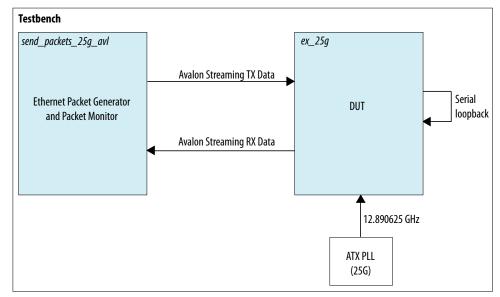

## Figure 10. Block Diagram of the 10G/25G Ethernet Single-Channel Design Example Simulation Testbench

## Table 5.Testbench Components

| Component                                    | Description                                                                                                                                                                           |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device under test (DUT)                      | The 25G Ethernet Intel FPGA IP core.                                                                                                                                                  |

| Reconfiguration Sequencer                    | Reconfigures the transceiver channel speed from 10 Gbps to 25 Gbps, and vice versa.                                                                                                   |

| Ethernet Packet Generator and Packet Monitor | <ul> <li>Packet generator generates frames and transmit to the DUT.</li> <li>Packet Monitor monitors TX and RX datapaths and displays the frames in the simulator console.</li> </ul> |

| ATX PLL                                      | Generates a TX serial clock for the Intel Stratix 10 10G/25G transceiver which is wrapped in the 25G Ethernet Intel FPGA IP core.                                                     |

*Note:* For the 10G/25G Ethernet single-channel design example with IEEE 1588v2 feature simulation testbench, refer to Figure 7 on page 13.

## 2.4.2. Simulation Design Example Components

####

| File Name                                             | Description                                                                                                                                                                                                               |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Testbench and Simulation Files                        |                                                                                                                                                                                                                           |  |

| basic_avl_tb_top.sv                                   | Top-level testbench file. The testbench instantiates the DUT, performs Avalon memory-mapped configuration on design components and client logic, and sends and receives packet to or from the 25G Ethernet Intel FPGA IP. |  |

| Testbench Scripts                                     |                                                                                                                                                                                                                           |  |

| run_vsim.do The ModelSim script to run the testbench. |                                                                                                                                                                                                                           |  |

| run_vcs.sh                                            | The Synopsys VCS script to run the testbench.                                                                                                                                                                             |  |

| run_ncsim.sh                                          | The Cadence NCSim script to run the testbench.                                                                                                                                                                            |  |

| run_xcelium.sh                                        | The Xcelium script to run the testbench.                                                                                                                                                                                  |  |

## 2.4.3. Test Case—Design Example Without the IEEE 1588v2 Feature

The simulation test case performs the following actions:

- 1. Instantiates 25G Ethernet Intel FPGA IP and ATX PLL.

- 2. Starts up the design example with an operating speed of 25G.

- 3. Waits for RX clock and PHY status signal to settle.

- 4. Prints PHY status.

- 5. Sends and receives 10 valid data on 25G speed.

- 6. Performs channel reset and switches to 10G speed.

- 7. Waits for RX clock and PHY status signal to settle.

- 8. Prints PHY status.

- 9. Sends and receives another 10 valid data on 10G speed.

- 10. Performs channel reset and switches to 25G speed.

- 11. Waits for RX clock and PHY status signal to settle.

- 12. Prints PHY status.

- 13. Sends and receives another 10 valid data on 25G speed.

- 14. Analyzes the results. The successful testbench displays "Simulation PASSED.".

The following sample output illustrates a successful simulation test run:

Waiting for RX alignment RX deskew locked RX lane alignmnet locked TX enabled \*\* Sending Packet 1... \*\* Sending Packet 3... \*\* Sending Packet 4...

\*\* Sending Packet 5...

\*\* Sending Packet 6...

\*\* Sending Packet 7...

\*\* Sending Packet 7...

\*\* Received Packet 1...

\*\* Received Packet 2...

\*\* Sending Packet 9...

\*\* Sending Packet 10...

\*\* Received Packet 3...

\*\* Received Packet 4...

\*\* Received Packet 5...

\*\* Received Packet 7...

\*\* Received Packet 8...

\*\* Received Packet 8...

\*\* Received Packet 9...

\*\* Received Packet 10...

Switching to 10G mode: 10G Reconfi Switching to 10G mode: 10G Reconfig start Switching to 10G mode: 10G Reconfig End Waiting for RX alignment RX deskew locked RX lane alignment locked RX lane alignment lockedTX enabled\*\* Sending Packet1....\*\* Sending Packet2....\*\* Sending Packet3....\*\* Sending Packet4....\*\* Sending Packet5....\*\* Sending Packet6....\*\* Sending Packet8....\*\* Sending Packet8....\*\* Sending Packet8....\*\* Sending Packet9....\*\* Sending Packet10....\*\* Received Packet9....\*\* Sending Packet10....\*\* Received Packet3....\*\* Received Packet5....\*\* Received Packet5....\*\* Received Packet5....\*\* Received Packet9....\*\* Received Packet8....\*\* Received Packet9....\*\* Received Packet9....\*\* Received Packet9....\*\* Received Packet10....Switching to 25G mode:25G Reconfil Switching to 25G mode: 25G Reconfig start Switching to 25G mode: 25G Reconfig End Waiting for RX alignment RX deskew locked RX lane alignment locked RX lane alignment locked TX enabled \*\* Sending Packet 1... \*\* Sending Packet 2... \*\* Sending Packet 3... \*\* Sending Packet 5... \*\* Sending Packet 6... \*\* Sending Packet 7... \*\* Sending Packet 8... \*\* Received Packet 1... \*\* Received Packet 9... \*\* Sending Packet 3... \*\* Received Packet 3... \*\* Received Packet 3... \*\* Received Packet 4... \*\* Received Packet 4... \*\* Received Packet \*\* Received Packet 5... \*\* Received Packet \*\* Received Packet \*\* Received Packet 7... 8... 9... \*\* Received Packet 10... \* \* \*\* Testbench complete. \* \*

## 2.4.4. Test Case—Design Example with the IEEE 1588v2 Feature

*Note:* For 10G/25G Ethernet single-channel design example with IEEE 1588v2 feature simulation testbench, refer to Figure 7 on page 13.

The simulation test case performs the following actions:

- 1. Instantiates 25G Ethernet Intel FPGA IP, ATX PLL, and IO PLL (sampling PLL).

- 2. Starts up the design example with an operating speed of 25G.

- 3. Waits for RX clock and PHY status signal to settle.

- 4. Prints PHY status.

- 5. Checks for 10 valid data on 25G speed.

- 6. Switches to 10G speed.

- 7. Waits for RX clock and PHY status signal to settle.

- 8. Prints PHY status.

- 9. Checks for another 10 valid data on 10G speed.

- 10. Switches to 25G speed once all 10 valid data passes.

- 11. Waits for RX clock and PHY status signal to settle.

- 12. Prints PHY status.

- 13. Checks for another 10 valid data on 25G speed.

- 14. Analyzes the results. The successful testbench displays "Simulation PASSED." when the PTP delay and offset data is within the threshold value.

The following sample output illustrates a successful simulation test run:

```

# Running at 25G mode...

#

# Waiting for RX alignment...

# iatpg_pipeline_global_en is set

# iatpg_pipeline_global_en is set

# RX deskew locked.

# RX lane aligmnent locked.

# Sending packets...

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000064457

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000064bb4

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000ffffffff8a2

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000643b5

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000000000520

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000634fb

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000000000

# Offset within tolerence range.

#

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000063f3b

```

Send Feedback

2. 10G/25G Ethernet Single-Channel Design Example for Intel Stratix 10 Devices 683252 | 2020.06.18

```

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000000000000

# Offset within tolerence range.

#

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000063a1a

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000006445a

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000063e95

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000648d5

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000643b5

# Offset within tolerence range.

#

# Finished sending packets.

# Switching to 10G mode: 10G Reconfig starts...

# Switching to 10G mode: 10G Reconfig End.

# Waiting for RX alignment...

# RX deskew locked.

# RX lane aligmnent locked.

# Configuring 1588 period...

# Configuring 1588 period done.

# Sending packets...

# Offset within tolerence range.

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000ffffffff99a0

# Offset within tolerence range.

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000ffffffffa66d

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000dfa97

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000006660

Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000001431

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000000005993

#

Offset within tolerence range.

#

#

```

```

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000002db7

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000ffffffffccc0

# Offset within tolerence range.

#

#

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000001431

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x000000000000ffffffff8006

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000000000e60e4

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000fffffffff320

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000dfa97

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000000005993

# Offset within tolerence range.

#

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000000874b

# Offset within tolerence range.

# Finished sending packets.

#

# Switching to 25G mode: 25G Reconfig start...

# Switching to 25G mode: 25G Reconfig end.

# Waiting for RX alignment...

# RX deskew locked.

# RX lane aligmnent locked.

# Configuring 1588 period...

# Configuring 1588 period done.

#

# Sending packets...

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000063c58

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x00000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000063c58

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000006502f

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000006502f

# Offset(sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000000000000

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x000000000000000006554d

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000064b10

# Offset within tolerence range.

```

#

```

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000064b10

#

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000064bb4

#

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000064bb4

#

# Offset within tolerence range.

# Delay (sec[95:48],ns[47:16],fns[15:0]): 0x0000000000000000065a6c

# Offset within tolerence range.

#

# Finished sending packets.

#

* *

#

#

** Testbench complete.

#

* *

```

## 2.5. Compilation

Follow the procedure in Compiling and Configuring the Design Example in Hardware on page 8 to compile and configure the design example in the selected hardware.

You can estimate resource utilization and Fmax using the compilation-only design example. You can compile your design using the **Start Compilation** command on the **Processing** menu in the Intel Quartus Prime Pro Edition software. A successful compilation generates the compilation report summary.

For more information, refer to *Design Compilation* in the *Compiler User Guide: Intel Quartus Prime Pro Edition*.

## **Related Information**

**Design Compilation**

In Compiler User Guide: Intel Quartus Prime Pro Edition

## 2.6. Hardware Testing

In the hardware design example, you can program the IP core in internal serial loopback mode and generate traffic on the transmit side that loops back through the receive side.

Follow the procedure at the provided related information link to test the design example in the selected hardware.

## **Related Information**

Testing the 25G Ethernet Intel FPGA IP Design in Hardware on page 10 More information on the procedure and hardware setup.

## 2.6.1. Test Procedure–Design Example Without the IEEE 1588v2 Feature

Follow these steps to test the design examples in hardware using PMA serial loopback:

- *Note:* The design example starts with default data rate of 25G.

- 1. Perform data rate switching to 10G:

- a. In Intel Quartus Prime Pro Edition software, go to **Tools ≻ In-System Sources & Probes Editor** tool to open the default source and probe GUI.

- b. Set the source bit[1] in source and probe to 1.

- 2. Perform data rate switching to 25G:

- a. In Intel Quartus Prime Pro Edition software, go to **Tools** ➤ **In-System Sources & Probes Editor** tool to open the default source and probe GUI.

- b. Set the source bit[1] in source and probe to 0.

- 3. Perform system reset release after executing the data rate reconfiguration:

- a. Click **Tools** ➤ **In-System Sources & Probes Editor** tool for the default Source and Probe GUI.

- b. Toggle the system reset signal (Source[0]) from 0 to 1 to apply the reset and return the system reset signal back to 0 to release the system from the reset state.

- c. Monitor the Probe signals and ensure that the status is valid.

- 4. Run the following commands in the system console to start the serial loopback test:

### Table 7.Command Parameters

| Parameter                                | Description                                          | Example Usage                                                             |

|------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------|

| chkphy_status <link<br>num&gt;</link<br> | Displays the clock frequencies and PHY lock status.  | <pre>% chkphy_status 0 # Check status of link 0</pre>                     |

| chkmac_stats                             | Displays the values in the MAC statistics counters.  | <pre>% chkmac_stats 1 # Checks mac<br/>statistics counter of link 1</pre> |

| clear_all_stats num>                     | Clears the IP core statistics counters.              | % clear_all_stats 1 # Clears<br>statistics counter of link 1              |

| start_gen <link num=""/>                 | Starts the packet generator.                         | % start_gen 1 # Begin packet<br>generation on link 1                      |

| stop_gen <link num=""/>                  | Stops the packet generator.                          | % stop_gen 1 # Stop packet<br>generation on link 1                        |

| loop_on <link num=""/>                   | Turns on internal serial loopback.                   | % loop_on 2 # Turn on internal<br>loopback on link 2                      |

| loop_off <link num=""/>                  | Turns off internal serial loopback.                  | <pre>% loop_off 2 # Turn off internal<br/>loopback on link 2</pre>        |

| reg_read <addr></addr>                   | Returns the IP core register value at <i>addr</i> >. | % reg_read 0x302 # Read IP CSR<br>register at address 302 of link 0       |

|                                          | •                                                    | continued                                                                 |

| Parameter                                 | Description                                                                | Example Usage                                                                                                                |

|-------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                                           |                                                                            | <pre>% reg_read 0x4542 # Read<br/>transceiver reconfiguration<br/>register at address 4542 of link<br/>0</pre>               |

| reg_write <addr><br/><data></data></addr> | Writes < <i>data</i> > to the IP core register at address < <i>addr</i> >. | <pre>% reg_write 0x30301 0x1 # Write<br/>0x1 to IP CSR scratch register at<br/>address 301 of link 3</pre>                   |

|                                           |                                                                            | <pre>% reg_write 0x34542 0x0 # Write<br/>0x0 to transceiver<br/>reconfiguration register at<br/>address 4542 of link 3</pre> |

- *Note:* a. For single-channel design, *<link num>* is always 0.

- b. For multi-channel design, *<link num>* is the channel number. The valid channel number range is 0 to 3.

- a. Type loop\_on <*link num*> to turn on the internal serial loopback mode.

- b. Type chkphy\_status <link num> to check the status of the PHY. The TXCLK, RXCLK, and RX status should have the same values shown below for a stable link:

## Figure 11. System Console Example Printout

Link: 0 Addr: 300 RX PHY Register Access: Checking Clock Frequencies (KHz) REFCLK :0 (KHZ) TXCLK :39065 (KHZ) RXCLK :39064 (KHZ) Link: 0 Addr: 300 RX PHY Status Polling Rx Frequency Lock Status 0x00000001 Mac Clock in OK Condition? 0x00000007 Rx Frame Error 0x0000000 Rx PHY Fully Aligned? 0x0000001

- c. Type clear\_all\_stats </ rows to clear TX and RX statistics registers.

- d. Type start\_gen <link num> to begin packet generation.

- e. Type stop\_gen <link num> to stop packet generation.

- f. Type chkmac\_stats </ink num> to read the TX and RX statistics counters. Make sure that:

- i. The transmitted packet frames match the received packet frames.

- ii. No error frames are received.

- g. Type loop\_off <*link num*> to turn off the internal serial loopback.

*Note:* The above configuration is applied to the default 25G mode for the first time.

## Figure 12. Sample Test Output—TX and RX Statistics Counters

| STATISTICS FOR BASE 2304 (Rx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fragmented Frames : 0<br>Jabbered Frames : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Any Size with FCS Err Frame : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Right Size with FCS Err Fra : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Multicast data Err Frames : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Broadcast data Err Frames : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Unicast data Err Frames : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Multicast control Err Frame : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Broadcast control Err Frame : 0<br>Unicast control Err Frames : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pause control Err Frames : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 64 Byte Frames : 375474                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |