# Altera Agilex 7 Issue in Accessing FPGA Fabric from HPS and Loading FPGA Bitfile

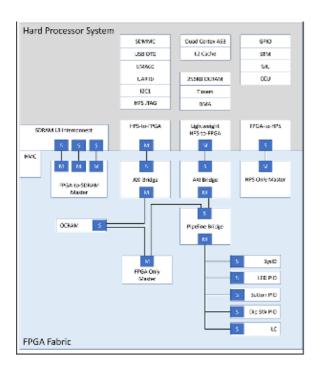

Objective: We are trying to access the FPGA fabric from the HPS region through the light weight AXI BUS.

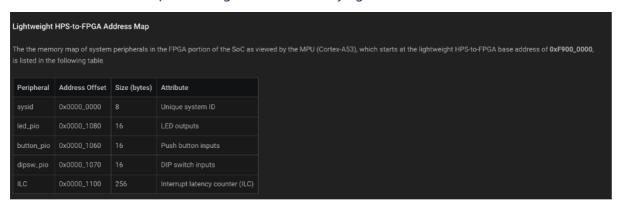

Below is the address map of the region that we are trying to access.

# **Environment:**

#### Hardware:

|      | Development Kit Version                                                                        | Ordering Code  | Device Part Number                    | Starting Serial Number |

|------|------------------------------------------------------------------------------------------------|----------------|---------------------------------------|------------------------|

| - 11 | Intel Agilex® 7 FPGA F-Series Transceiver-SoC Development Kit (Production 2 P-Tiles & E-Tiles) | DK-SI-AGF014EB | AGFB014R24B2E2V<br>(Power Solution 2) | 00205001               |

## ATF version:

NOTICE: BL31: v2.9.0(release):QPDS23.3\_REL\_GSRD\_PR-dirty

NOTICE: BL31: Built : 08:59:38, Nov 12 2023

## Uboot version:

```

SOCFPGA_AGILEX # version

U-Boot 2023.04-28289-gdf8159c1e7-dirty (Nov 12 2023 - 13:12:38 +0530)socfpga_agilex

aarch64-none-linux-gnu-gcc (GNU Toolchain for the Arm Architecture 11.2-2022.02 (arm-11.14)) 11.2.1 20220111

GNU ld (GNU Toolchain for the Arm Architecture 11.2-2022.02 (arm-11.14)) 2.37.20220122

```

## GSRD from Rocketboard:

- 1. SOF

- 2. Uboot SPL

#### Issue:

1. When trying to access the FPGA memory region 0xF900\_0000 from the Uboot using the "md" command, the FPGA+Uboot crashes.

```

SOCFPGA_AGILEX # md f9000000

"Synchronous Abort" handler, esr 0x96000010

elr: 00000000002971f4 lr : 0000000000297144 (reloc)

elr: 000000007ff8e1f4 lr: 000000007ff8e144

x0 : 0000000000000000 x1 : 000000007faef268

x4 : 00000000000000000 x5 : 000000007faef260

x6 : 00000000000000000 x7 : 000000007faef1b0

x8 : 00000000000000010 x9 : 00000000000000008

x10: 00000000ffffffd8 x11: 00000000000000000

x12: 000000000001869f x13: 000000007faef4d8

x14: 000000007faef5e0 x15: 00000000000000021

x16: 000000007ff13324 x17: 0000000000000000

x18: 000000007faf4da0 x19: 00000000000000004

x20: 0000000000000004 x21: 00000000000000004

x22: 00000000f9000000 x23: 000000007faef269

x24: 00000000000000000 x25: 000000007faef218

x26: 000000007ffa7a26 x27: 00000000000000008

x28: 00000000000000004 x29: 000000007faef1b0

Code: 2a0403f3 17ffffcb 7100129f 54000181 (b94002c3)

Resetting CPU ...

### ERROR ### Please RESET the board ###

```

2. Wherein if we try to access address map in HPS we are able to read it using the Uboot "md" command, e.g. UART at 0xFFC0 2000

```

SOCFPGA_AGILEX # md 0xffc02000

ffc02000: 00000000 00000000 000000c1 00000003

ffc02010: 00000003 00000000 00000010 00000000

. . . . . . . . . . . . . . . . .

ffc02070: 00000000 00000000 00000000 00000002

ffc02080: 00000001 00000000 00000000 00000001

ffc02090: 00000000 00000000 00000001 00000000

ffc020f0: 00000000 00083f32 3331352a 44570110

....2?..*513..WD

```

3. As per the HPS Address Map and Register definition: <a href="https://www.intel.com/content/www/us/en/programmable/hps/agilex/hps.html#topic/gfi1561688682142.html">https://www.intel.com/content/www/us/en/programmable/hps/agilex/hps.html#topic/gfi1561688682142.html</a>

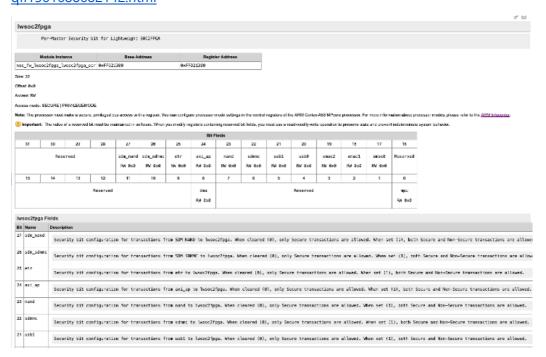

# The bit 24 in the lwsoc2fpga register should be set:

4. From the Uboot arch/arm/dts/socfpga\_soc64\_u-boot.dtsi file we can confirm this:

```

noc_fw_lwsoc2fpga_lwsoc2fpga_scr@ffd21300 {

reg = <0xffd21300 0x00000004>;

/* Disable lightweight soc2fpga security access */

intel,offset-settings = <0x00000000 0x0ffe0101 0x0ffe0101>;

u-boot,dm-pre-reloc;

```

5. In order to cross check, we enabled the SMC (Secure Monitor Call) in the Uboot and confirmed it.

```

[SOCFPGA_AGILEX # smc ${smc_fid_rd} FFD21300

EL = 2

Res: 0 268304641 4291957504 0

```

The value 268304641 is in decimal and is the value contained in the register 0xFFD2\_1300.

Expanded the value 268304641 in hexadecimal equivalent = 0x0FFE\_0101

6. Few other registers were also not accessible from the Uboot console using SMC command. In order to access then I had to include the registers in the below file:

plat/intel/soc/common/socfpga\_sip\_svc.c in the function

static int is\_out\_of\_sec\_range(uint64\_t reg\_addr)

as:

7. I have confirmed that we are in EL2 in the Uboot console by adding the below code snippet:

```

register uint64_t x0 __asm__ ("x0");

__asm__ ("mrs x0, CurrentEL;" : : : "%x0");

printf("EL = %"PRIu64" \n", x0 >> 2);

```

Output:

EL = 2

But still we are not able to access the address map 0xF900\_0000 and few other registers.

Loading the FPGA bitfile using TFTP:

1. tftp \${loadaddr} flash\_image.core.rbf -> the .rbf file is the bitfile that is generated using the Quartus Program File Generator

2. fpga load 0 \${loadaddr} \${filesize}

After loading the FPGA bitfile we get the success message:

```

SOCFPGA_AGILEX # fpga load 0 ${loadaddr} ${filesize}

..FPGA reconfiguration OK!

```

3. Bridge enable command doesn't throw any error: bridge enable

```

SOCFPGA_AGILEX # bridge enable

SOCFPGA_AGILEX #

```

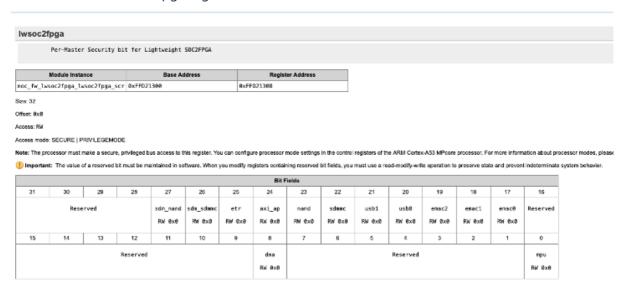

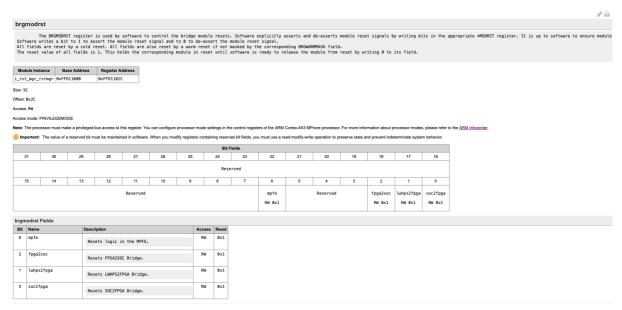

Resetting the brgmodrst:

I enabled the SMC command in the Uboot and tried to the steps that you have described:

Without the SMC command we can't access the register 0xFFD1102C and many other registers.

# Enabling the AXI bus:

I have enabled the AXI bus command in the Uboot.

The command "AXI bus" doesn't show any AXI bus information.

```

SOCFPGA_AGILEX # axi

axi - AXI sub-system

Usage:

axi bus - show AXI bus info

axi dev [bus] - show or set current AXI bus to bus number [bus]

axi mus size addr [# of objects] - read from AXI device at address [addr] and data width [size] (one of 8, 16, 32)

axi mw size addr value [count] - write data [value] to AXI device at address [addr] and data width [size] (one of 8, 16, 32)

SOCFPGA_AGILEX # axi bus

EL = 2

SOCFPGA_AGILEX #

```

I enabled the SMC command in the Uboot and tried to the steps that you have described:

Without the SMC command we can't access the register 0xFFD1102C and many other registers.

```

SOCFPGA_AGILEX # smc ${smc_fid_rd} 0xffd1102c

EL = 2

Res: 0 7 4291891244 0

SOCFPGA_AGILEX # smc ${smc_fid_wr} 0xffd1102c 0x000000000

EL = 2

Res: 0 0 4291891244 0

SOCFPGA_AGILEX # smc ${smc_fid_rd} 0xffd1102c

EL = 2

Res: 0 0 4291891244 0

```

But, still not able to access the address map 0xF900\_0000.

```

SOCFPGA_AGILEX # md f9000000

"Synchronous Abort" handler, esr 0x96000010

elr: 00000000002971f4 lr : 0000000000297144 (reloc)

elr: 000000007ff8e1f4 lr : 000000007ff8e144

x0 : 00000000000000009 x1 : 000000007faef268

x6 : 000000000000000000000000000000007faef1b0

x10: 00000000ffffffd8 x11: 00000000000000000

x12: 00000000001869f x13: 0000000000000

x16: 000000007ff13324 x17: 0000000000000

x18: 000000007faf4da0 x19: 0000000000000004

x20: 00000000000000004 x21: 00000000000000004

x22: 00000000f9000000 x23: 000000007faef269

x24: 00000000000000000 x25: 000000007faef218

x26: 000000007ffa7a26 x27: 00000000000000008

x28: 0000000000000000 x29: 000000007faef1b0

Code: 2a0403f3 17ffffcb 7100129f 54000181 (b94002c3)

Resetting CPU ...

```

I reset the BRGWARMMASK register:

| Module Instance  | Base Address | Register Address |  |  |

|------------------|--------------|------------------|--|--|

| i_rst_mgr_rstmgr | 0xFFD11000   | 0xFFD1104C       |  |  |

```

SOCFPGA_AGILEX # smc ${smc_fid_rd} 0xffd1104c

EL = 2

Res: 0 7 4291891276 0

SOCFPGA_AGILEX # smc ${smc_fid_wr} 0xffd1104c 5

EL = 2

Res: 0 5 4291891276 0

```

No success.

I modified the Agilex7 default configuration to pull in the .RBF file from the MMC as instructed like in the Rocketboard website:

I just read the register fpga\_config:

```

1617920 bytes read in 77 ms (20 MiB/s)

FPGA not ready. Bridge reset aborted!

..FPGA reconfiguration OK!

[SOCFPGA_AGILEX # smc ${smc_fid_rd} 0xffd120dc

EL = 2

Res: 0 3 4291895516 0

```

## Reference:

| pga | _config Fields |                             |        |      |

|-----|----------------|-----------------------------|--------|------|

| Bit | Name           | Description                 | Access | Rese |

| 1   | early_usermode | FGPA configuration complete | RO     | 0×0  |

| 0   | fpga_complete  | FGPA configuration complete | RO     | 0×0  |

The clocks are also enabled:

Res: w Zw4r 4Z91007ZZ0 w

SOCFPGA\_AGILEX # smc \${smc\_fid\_rd} 0xffd100

EL = 2

Res: 0 127 4291887140 0

SOCFPGA\_AGILEX #

## Reference:

|    | Bit | Fields |               |              |         |           |           |      |

|----|-----|--------|---------------|--------------|---------|-----------|-----------|------|

| 25 | 24  | 23     | 22            | 21           | 20      | 19        | 18        |      |

|    | Res | served |               |              |         |           |           |      |

| 8  | 8   | 7      | 6             | 5            | 4       | 3         | 2         |      |

|    |     |        | s2fuser0clken | cstimerclken | csclken | l4spclken | l4mpclken | l4ma |

|    |     |        | RW 0×1        | RW 0×1       | RW 0x1  | RW 0x1    | RW 0×1    | R    |

# Question:

- 1. What wrong I am doing?

- 2. How can we access the FPGA address map from the HPS using the light weight AXI bus?