## 1.3 Power-on Timing

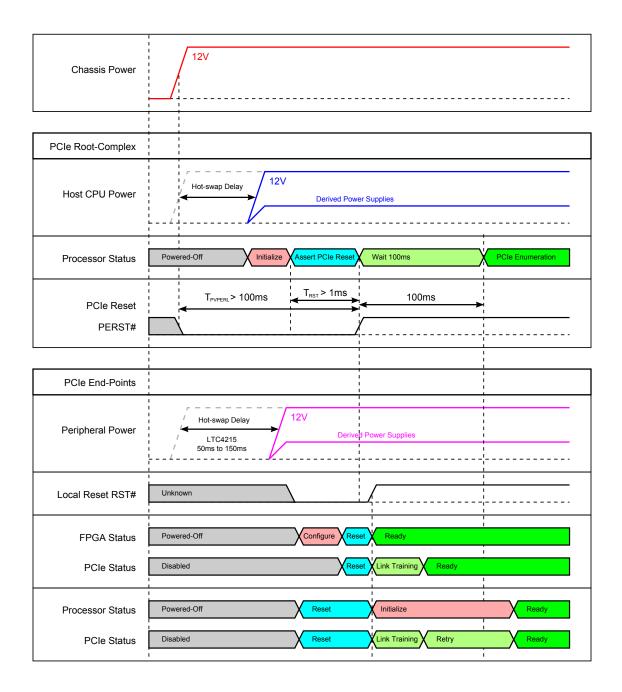

Figure 1 shows a diagram of the power-on timing for the TS4 board. The power-on sequence is;

- The user turns on the main power switch, which enables the chassis 12V power.

- The host CPU (PCIe root-complex) powers up, initializes, asserts the PCIe reset signal, waits 100ms, and then enumerates the PCIe bus (these tasks are typically implemented by firmware in the host CPU BIOS or bootloader).

- The peripheral board PCIe end-point has two implementation options;

- An FPGA-based PCIe end-point (eg., Altera Cyclone IV GX [2]).

The peripheral board powers up, the FPGA configures prior to PCIe reset deassertion, when reset deasserts, the PCIe end-point begins link training, and within 20ms is ready for PCIe accesses.

The configuration time for a Cyclone IV GX EP4CGX15 configured via Fast Passive Parallel (FPP) mode using a 66MHz clock is; 3ms power-supply ramp + 9ms power-on-reset delay + 3,805,568-bits/66MHz = 70ms.

- A processor-based PCIe end-point (eg., Freescale MPC8308 [18]).

The peripheral board powers up, when reset deasserts, the PCIe end-point begins link training, and within 20ms is ready for PCIe accesses. If the processor software has not enabled the PCIe end-point by the time the host attempts a configuration space access, those accesses will receive a PCIe retry response. The end-point is allowed to issue retry responses for up to one second from the deassertion of PCIe reset.

The power-on timing in Figure 1 is specified in the following references;

- PCI Express Specification [11]:

- A component must enter link training within 20ms of the deassertion of PERST# (p406 [11]).

- System software must wait 100ms from the deassertion of PERST# before issuing configuration space accesses (p406 [11]).

- System software must allow 1.0s before it can determine that configuration space accesses have failed (p406 [11]), i.e., an end-point can issue a PCIe retry for up to 1.0s.

- $-T_{\text{PVPERL}}$  defines the time PERST# must remain active after power becomes valid.  $T_{\text{PERST}}$  defines the time PERST# must remain active when asserted. These timing parameters are platform specific (p407 [11]).

- CPCI-S.0 Specification [12]:

- The system slot must drive PCIe reset low once the main 12V supply reaches 5V (p80 [12]).

- $-T_{RST} > 1ms$  (Table 13, p80 [12]). This parameter is the platform-specific  $T_{PERST}$  defined in the PCI Express specification.

- PCI Express Card Electromechanical (CEM) specification [10]

- This specification discusses the implementation of desktop form-factor PCIe systems (also known as ATX or Advanced Technology eXtended motherboards). CPCI-S.0 power supplies are based on ATX power supplies, so the power supply discussion in this specification is relevant.

- Deassertion of PERST# occurs  $T_{PVPERL} = 100$ ms after power is stable (p22 [10]). Figure 1 is similar to Figure 2-10 on p23 [10].

- The Intel ATX power supply design guide specifies  $100 \text{ms} < T_{\text{PVPERL}} < 500 \text{ms}$  (see the T3 parameter in Figure 7 p25 and Table 15 p26 [7]).

Figure 1: CPCI-S.0 power-on timing.

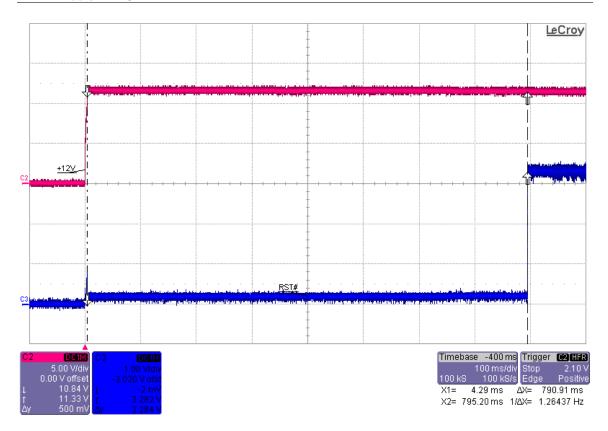

Figure 2: MEN G20 CPCI-S.0 host CPU board 12V to PCIe reset power-on timing.

Figure 2 shows the power-on timing of the MEN G20 CPCI-S.0 CPU (image courtesy of Stephen Cunha, MEN Microelectronics, 7/11/2012). PCIe reset deasserts approximately 800ms after the 12V supply is valid. This provides sufficient time for a PCIe end-point to be implemented using either an FPGA or processor.

## References

- Altera Corporation. MAX II Device Handbook (version 3.3), November 2009. (max2\_mii5v1.pdf).

- [2] Altera Corporation. Cyclone IV Handbook (version 1.6), November 2011. (cyclone4-handbook.pdf).

- SFF Committee. SFF-8436 Specification for QSFP+ 10Gbps 4× Pluggable Transceiver (Revision 4.2), March 2012. (SFF-8436.PDF).

- [4] FTDI. FT245BL USB FIFO (USB-Parallel) IC (version 1.7). Data sheet, 2005. (DS\_FT245BL.pdf).

- [5] FTDI. FT2232H Dual High Speed USB to Multipurpose UART/FIFO IC (version 2.21). Data sheet, 2012. (DS\_FT2232H.pdf).

- [6] Texas Instruments. AM335x ARM Cortex-A8 Microprocessors (MPUs). Data sheet, 2012. (sprs717d.pdf).

- [7] Intel Corporation. ATX12V Power Supply Design Guide (version 2.2), March 2005. (ATX12V\_PSDG\_2\_2\_public\_br2.pdf).

- [8] Marvell. 88E1111: Integrated 10/100/1000 Ultra Gigabit Ethernet Transceiver. Data sheet, 2006.

- [9] Panasonic. ERJM03/ERJM1W Low resistance value chip resistors (current sensing resistors), 2012. (AOA0000CE7.pdf).

- PCISIG. PCI Express Card Eletromechanical Specification Revision 2.0, April 2007. (http://www.pcisig.org/).

- [11] PCISIG. PCI Express Base Specification Revision 2.1, March 2009. (http://www.pcisig.org/).

- [12] PICMG. CompactPCI Serial Specification (PICMG CPCI-S.0 R1.0), March 2011. (http://www.picmg.org/).

- [13] International Rectifier. IRF6618: DirectFET Power MOSFET, August 2007. (irf6618pbf.pdf).

- [14] International Rectifier. IRF6718: DirectFET Power MOSFET, July 2011. (irf6718l2pbf.pdf).

- [15] Renesas. RJK0301DPB: Silicon N-Channel Power MOSFET, April 2006. (rej03g1338\_rjk0301dpbds.pdf).

- [16] Fairchild Semiconductor. NC7SZ157: TinyLogic UHS 2-input non-inverting multiplexer. Data sheet, 2009. (NC7SZ157.pdf).

- [17] Fairchild Semiconductor. NC7SZ125: TinyLogic UHS buffer with three-state output. Data sheet, 2010. (NC7SZ125.pdf).

- [18] Freescale Semiconductor. MPC8308 PowerQUICC II Pro Processor Reference Manual. Reference manual, April 2010. (MPC8308RM.pdf).

- [19] Freescale Semiconductor. MPC8308 PowerQUICC II Pro Processor Hardware Specification. Data sheet, August 2011. (MPC8308EC.pdf).