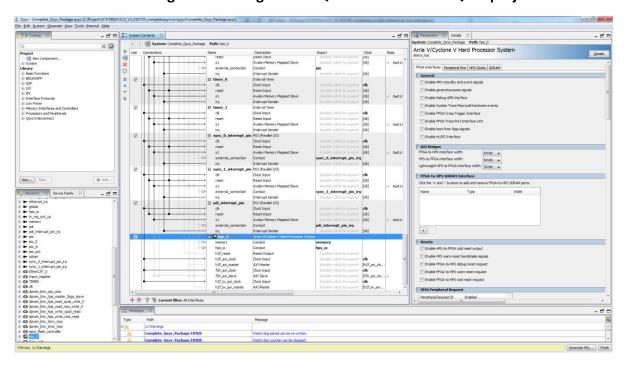

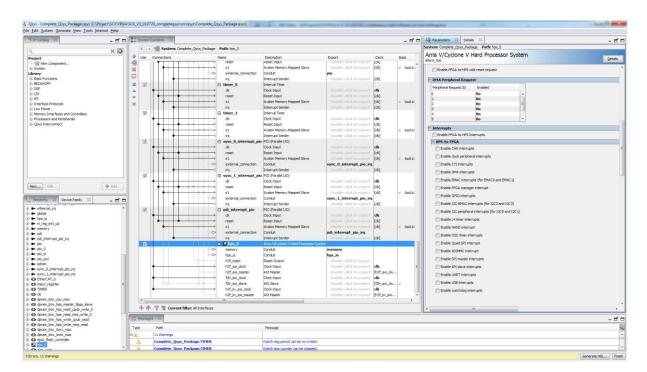

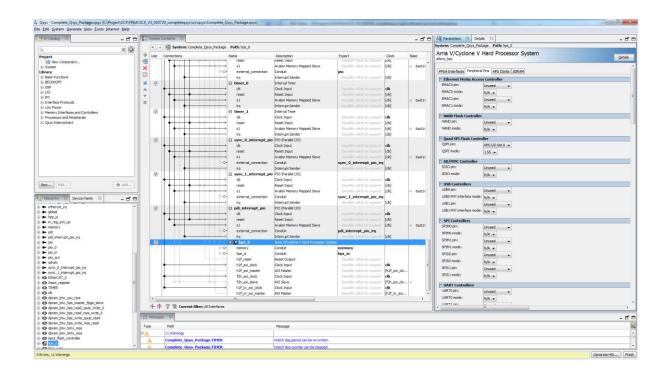

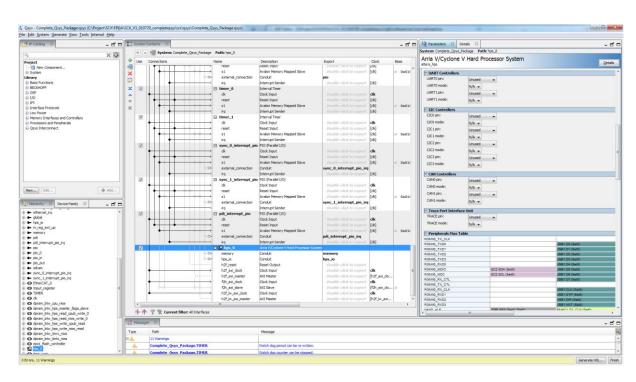

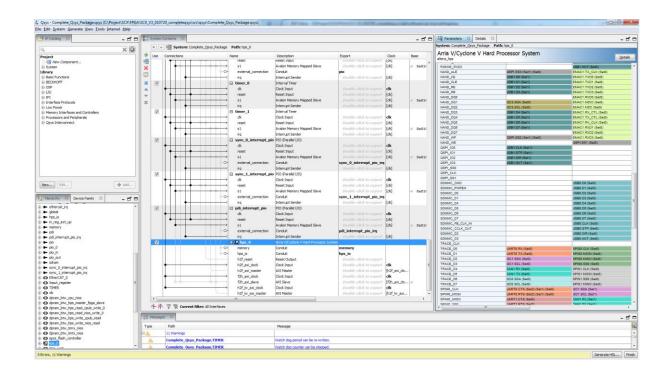

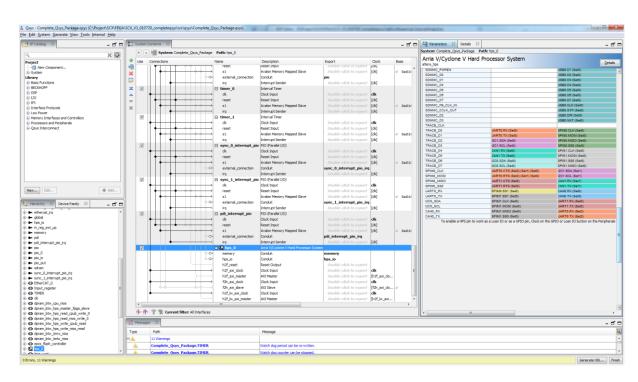

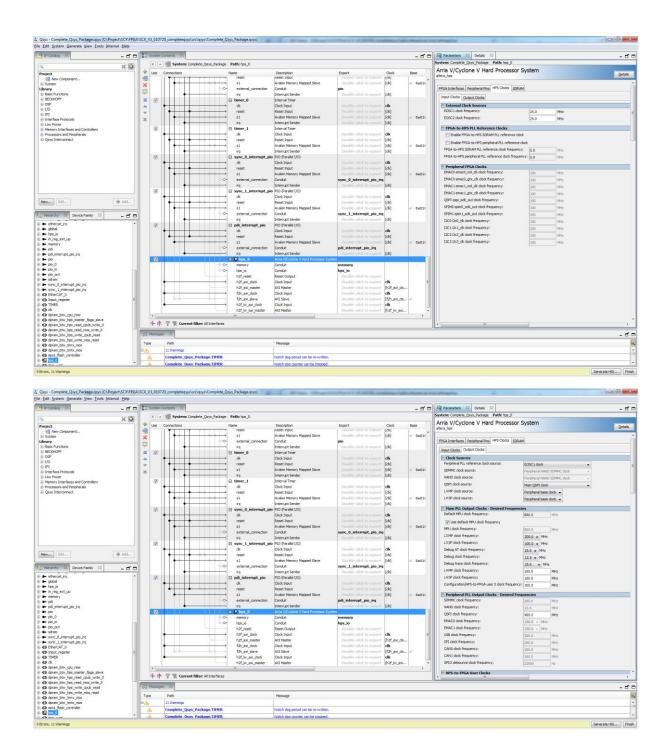

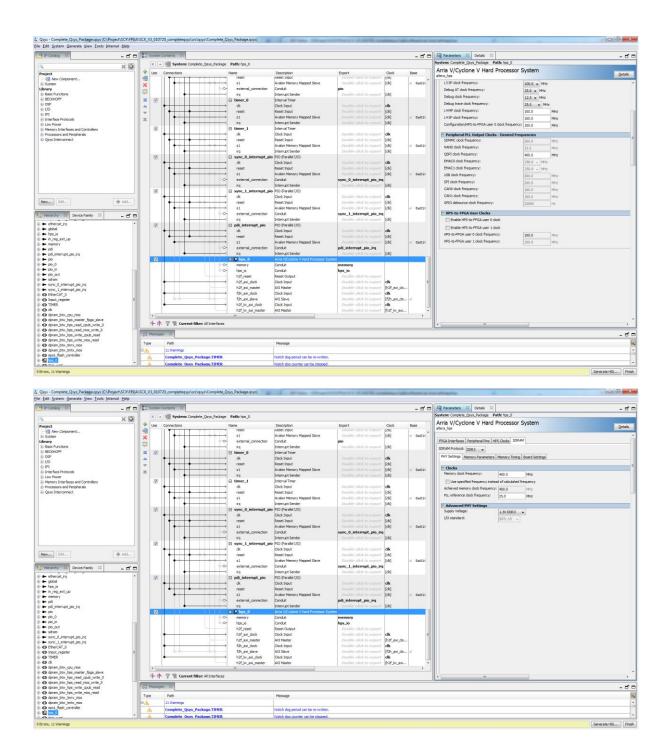

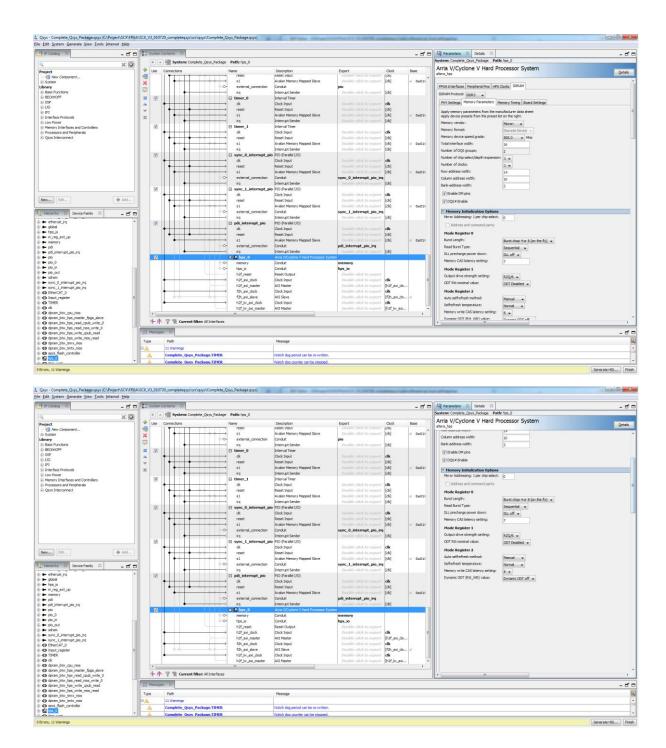

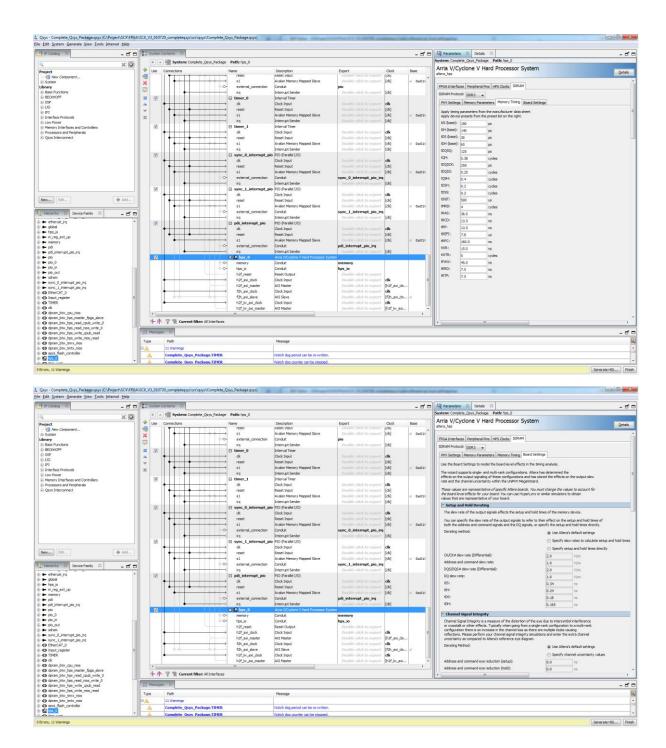

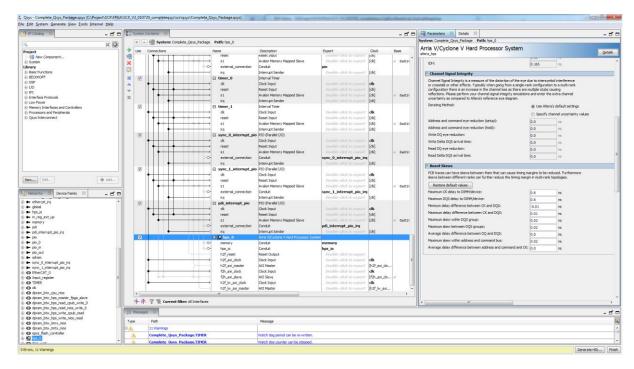

HPS in the qsys and its settings

We are using almost empty hps with only basic settings for the DDR3.

Following is the settings of the QSPI and the HPS in QSYS project.

As we are flashing from QSPI we need only QSPI flash controller

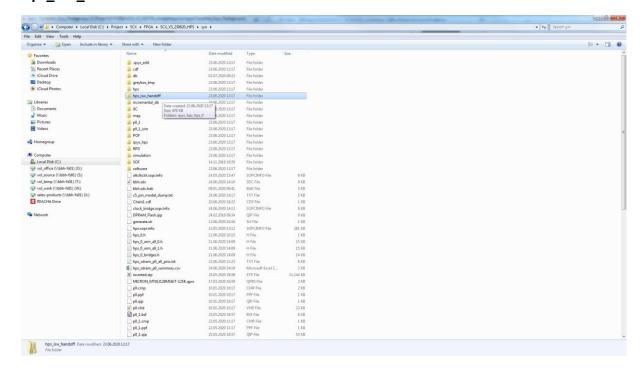

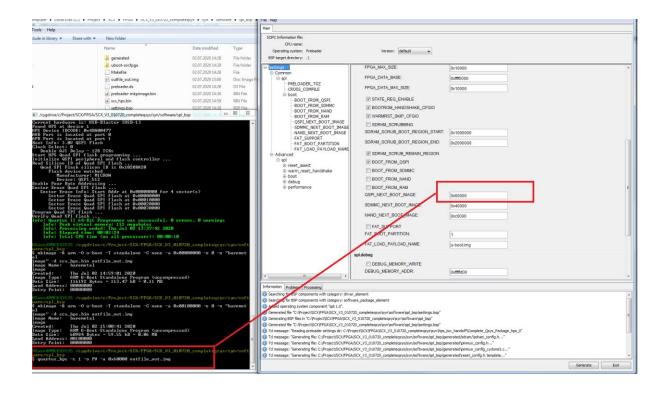

After compiling the FPGA we get the following folder.

## Hps\_isw\_handoff

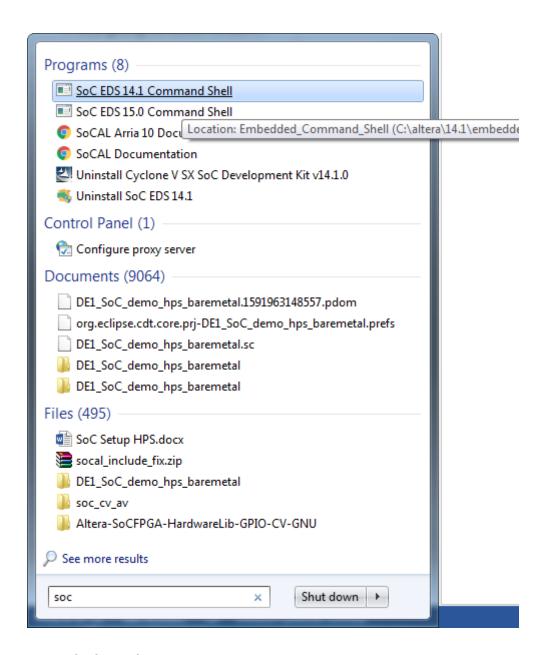

2. Now open SoC command shell

3. OPEN the bsp-editor By using bsp-editor&

```

- - X

/cygdrive/c/Project/SCX/FPGA/SCX_V3_010720_completeqsys/syn/software/spl_bsp

Created: Thu Jul 02 15:00:41 2020

Image Type: ARM U-Boot Standalone Program (uncompressed)

Data Size: 60984 Bytes = 59.55 kB = 0.06 MB

Load Address: 00100000

Entry Point: 00000000

image

aeed@MCE43535 /cygdrive/c/Project/SCX/FPGA/SCX_U3_010720_completeqsys/syn/soft

quartus_hps -c 1 -o PV -a 0x60000 outfile_out.img

Ξ

Saeed@MCE43535 /cygdrive/c/Project/SCX/FPGA/SCX_U3_010720_completeqsys/syn/soft

are/spl_bsp

bsp-editor&_

```

4. The rules of Preloader

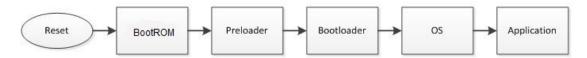

There are four stages of the hard processor system (HPS) booting process; the preloader is the second stage.

Figure 8-1: Typical Boot Flow

The Preloader configures the HPS component based on the information from the handoff folder, initializes the SDRAM and then loads the next stage of the boot process into SDRAM and passes control to it.

The preloader can directly load your final application for Bare Metal applications and simple RTOSes.

Typically, a boot ROM loads the preloader from a flash device into the on-chip RAM and executes the preloader. The preloader can also be executed directly from the FPGAmemory.

## 5. Handoff Files (this files is generated by Qsys)

#### Hardware Handoff Files

Use the Qsys system integration tool in the Quartus II software to generate a set of handoff files containing the hardware information required by the preloader.

The handoff files from the Qsys compilation are located in the *quartus project* directory>/hps\_isw\_handoff/<hps entity name> directory (where hps entity name is the HPS component name in Qsys).

**Note:** You must update the hardware handoff files and regenerate the preloader support package each time a hardeare change impacts the HPS, such as after pin multiplexing or pin assignment.

In this example, you will re-create the **Preloader** in the folder *<SoC EDS installation directory>*/**examples/** hardware/cv\_soc\_devkit\_ghrd/software/spl\_bsp.

The screen snapshots presented in this section were created using the Windows version of SoC EDS, but the example can be run in a very similar way on a Linux host PC.

The steps to create the Preloader are:

- Start an Embedded Command Shell by executing <SoC EDS installation directory>\Embedded\_Command\_ Shell.bat.

- 2. Run the command, bsp-editor. The BSP Editor dialog box appears.

Note: The tool that generates a preloader support package is the BSP Editor, also used to generate BSPs for other Altera products.

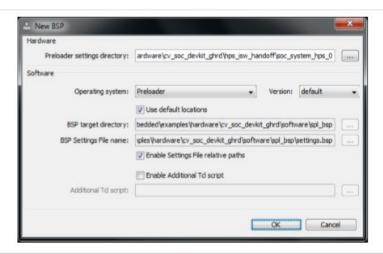

- 3. Select File > New BSP. The New BSP dialog opens.

- 4. Click the "..." button to browse for the Preloader settings directory in the New BSP dialog box.

- Browse <SoCEDS folder>\examples\hardware\cv\_soc\_devkit\_ghrd\hps\_isw\_handoff\soc\_system\_hps\_0 for the hardware handoff folder. The rest of the Preloader settings are populated automatically.

Figure 5-2: Populated Options in the New BSP window

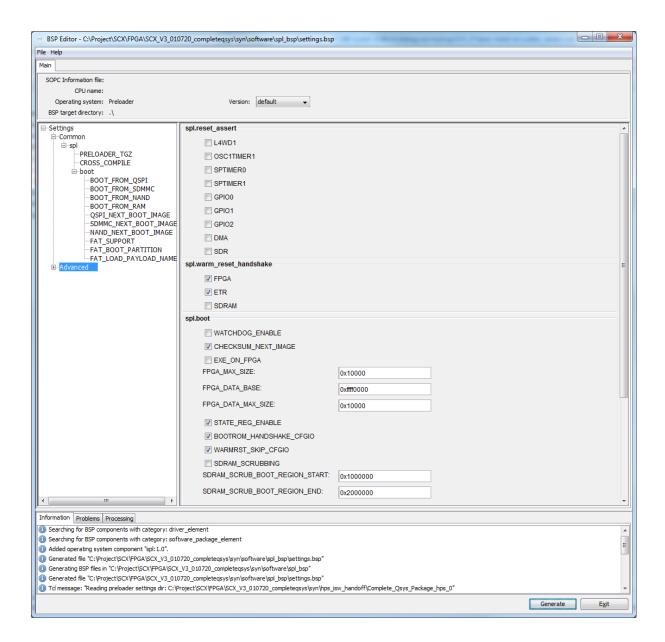

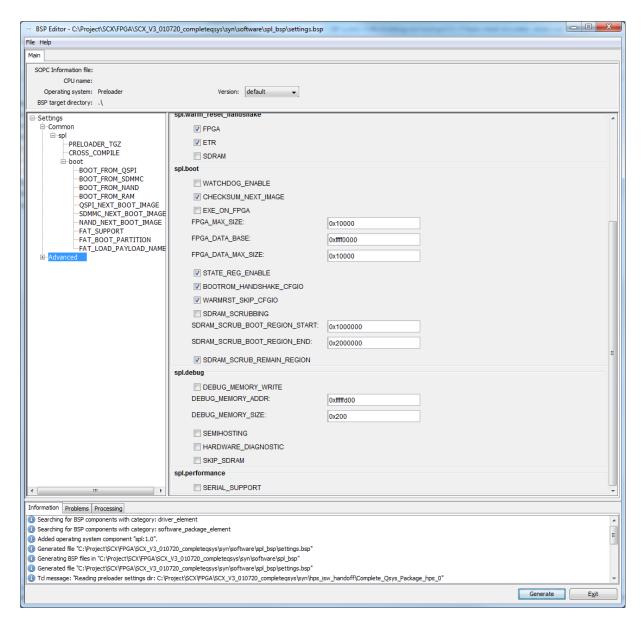

- 7. Click Generate in the BSP Editor dialog box to generate the Preloader files.

- 8. Click Exit in the BSP Editor dialog box to exit the application.

- 9. In the Embedded Command Shell, execute the following commands:

- cd <SoC EDS installation directory>\examples\hardware\cv\_soc\_devkit\_ghrd\software\spl\_bsp

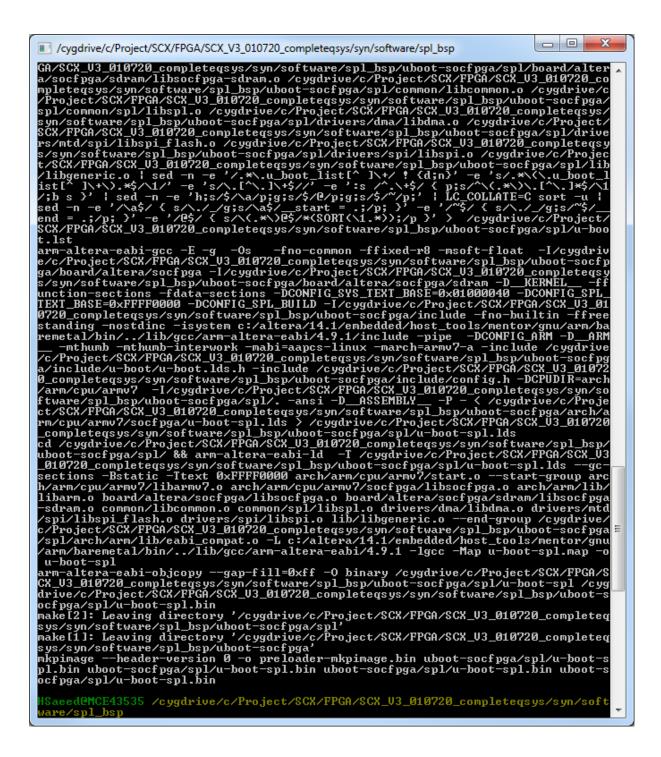

- make

10. The Preloader is ready to be used in the above folder. Some of the more relevant files that are created:

- preloader-mkpimage.bin Preloader with the proper header to be loaded by BootROM

- uboot-socfpga \ spl \ u-boot- spl Preloader ELF file, to be used for debugging purposes

- uboot-socfpga \tools\mkimage.exe Utility to add the header needed by the Preloader to recognize

the next boot stage

### 2. see the following boot loader settings for booting from qspi

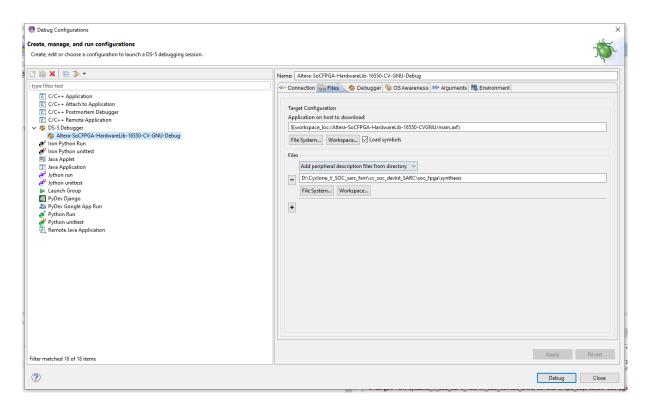

# 3. For the debugging, the preloader ELF file (u-boot-spl) should be imported to the DS-5 debugger

after generate the preloader, use the embedded shall to generate the preloader ELF file.

First, specify the path of preloader (cd: .....) that it is already generated, then write "make clean" or "make clean-all", then "make uboot".

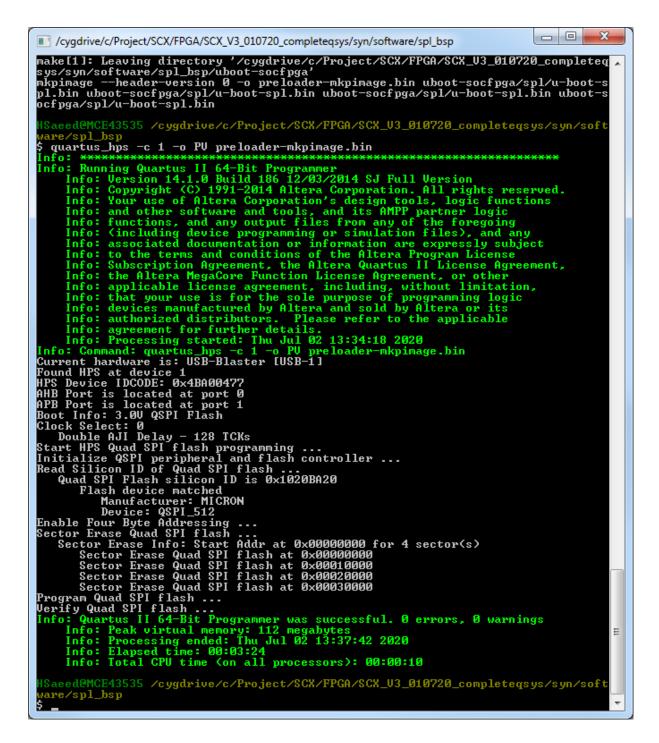

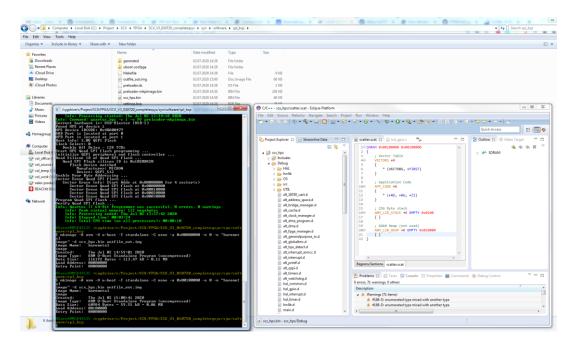

4. Flash this generated preloader-mkpimage.bin to QSPI flash using the following command

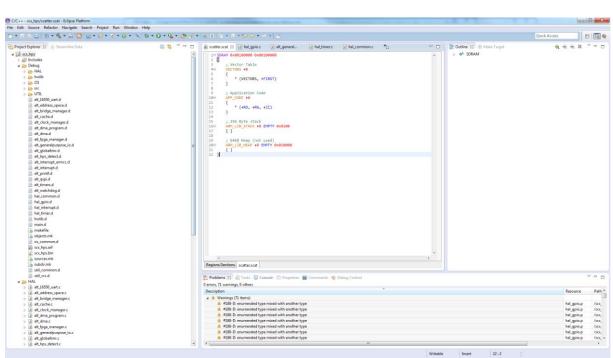

5. Add the scatter file to your DS-5 project. The scatter file which we are using will support the interrupts too. The interrupt is also called from the DDR3 memory. It makes no difference in the time If we use the onchip scatter file for interrupt or the DDR3 scatter file for the interrupt. The problem to use onchip scatter with DDR3 scatter makes a very big out.bin file.

Abbildung 1: DDR3 interrupt

Abbildung 2: onchip for interrupt and the remaining program from DDR3

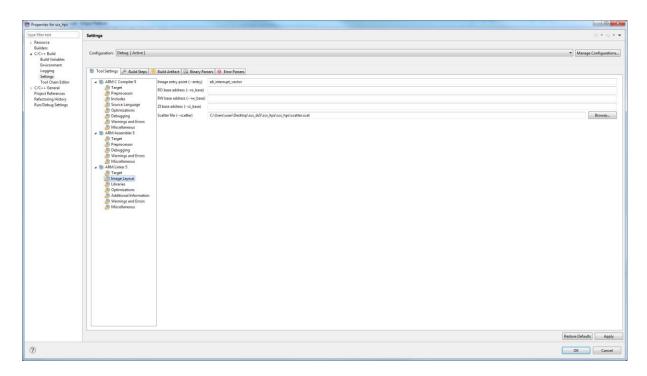

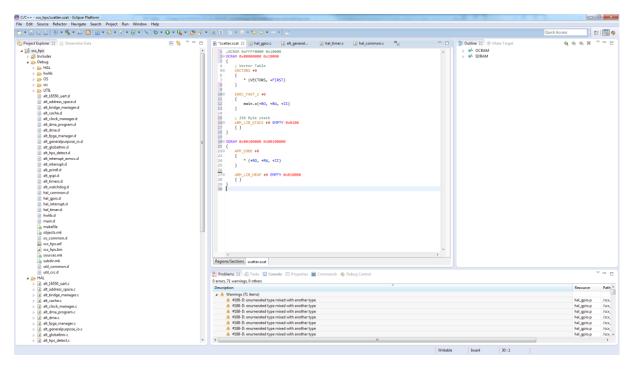

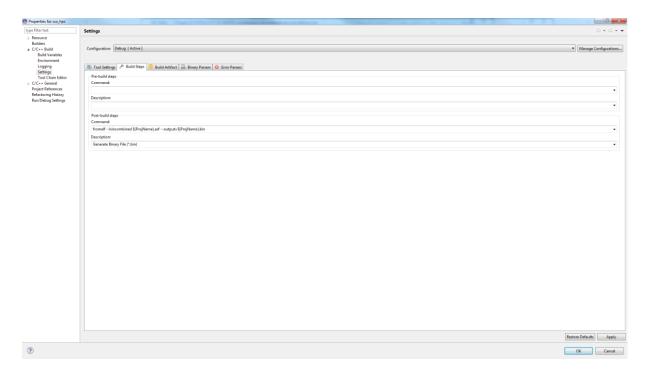

6. In the DS-5 the project settings use the fromelf as shown below this will generate the binary file after you compile the baremetal code.

# 7. After getting the out.bin file add the boot header using the following command

mkimage -A arm -O u-boot -T standalone -C none -a 0x02100000 -e 0 -n "baremetal image" - d hello\_world.bin hello\_world.img

here "0x02100000" depends on the scatter file used in the project

I used the following command for the scatter file shown in Abbildung 2

```

/cygdrive/c/Project/SCX/FPGA/SCX_V3_010720_completeqsys/syn/software/spl_bsp

mkpimage --header-version 0 -o preloader-mkpimage.bin uboot-socfpga/spl/u-boot-s

pl.bin uboot-socfpga/spl/u-boot-spl.bin uboot-socfpga/spl/u-boot-spl.bin uboot-s

ocfpga/spl/u-boot-spl.bin

Saced@MCE43535 /cygdrive/c/Project/SCX/FPGA/SCX_V3_010720_completeqsys/syn/soft

quartus_hps -c 1 -o PV preloader-mkpimage.bin

Saeed@MCE43535 /cygdrive/c/Project/SCX/FPGA/SCX_U3_010720_completeqsys/syn/soft

mkimage –A arm –O u-boot –T standalone –C none –a 0x00000000 –e 0 –n "baremet

image" -d scx_hps.bin outfile_out.img_

```

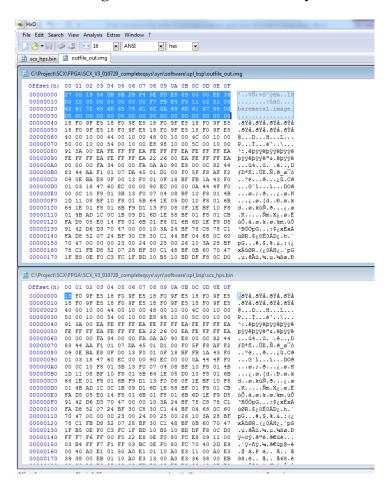

8. After executing command for the shown scatter file will add the header information and generate outfile out.img

## The following header is added in the binary file

9. Flash this image which we just created on the QSPI using the following command.

Power on the device and it should start up with your application program.

Extra information if needed.

The preloader ELF file is now generated and can be imported to the DS-5 debugger through a makefile (available in my DS-5 project).

You need then to load the (.svd) file to have the features of accessing to soft IP register.

This file is also generated after the Qsys is compiled. To load this file (.svd) to DS-debugger, open (Debugger configuration -- > files ), and load the (.svd file) which located in synthesis folder (please see the next screen shot).

The following handoff files are created when the hardware project is compiled:

- Handoff folder contains information about how the HPS component is configured, including things like which peripherals are enabled, the pin muxing and IOCSR settings, memory parameters, etc

- .svd file contains descriptions of the HPS registers and of the soft IP registers on FPGA side

- .sopcinfo file contains a description of the whole system

The handoff folder is used by the preloader generator to create the Preloader.

The <u>.svd</u> file contains the description of the registers of the HPS peripheral registers and registers for soft IP components in the FPGA portion of the SoC. This file is used by the ARM DS-5 Debugger to allow these registers to be inspected and modified by the user.

SOPC Information (.sopcinfo) file, containing a description of the entire system, is used by the Device Tree Generator to create the Device Tree used by the Linux kernel.

**Note:** The soft IP register descriptions are not generated for all soft IP cores.

Loading the . SVD file

Additional information about Boot ROM, Preloader, and BootLoader

The following figure depicts the typical boot flow:

Figure 1. Typical Boot Flow

#### **Boot ROM**

The HPS boot process starts when the processor is released from reset, and jumps to the reset vector address, located in the Boot ROM address space. Typically, the main responsibilities of the Boot ROM are:

- Detect the selected boot source

- Perform minimal HPS initialization

- Load the next boot stage (typically the Preloader) from Flash to OCRAM and jump to it

The behavior of the Boot ROM is influenced by the BSEL and CSEL options, and also by the registers in System Manger (for RAM boot) as shown later in the document. For the scenarios where the next boot stage is located in Flash, the Boot ROM can use up to four different images:

#### Preloader

Typically, the main responsibilities of the Preloader are:

- Perform additional HPS initialization

- Bring up SDRAM

- $\bullet\,$  Load the next boot stage from Flash to SDRAM and jump to it

Currently, two different Preloader options are available:

- SPL part of U-Boot. Provided with SoC EDS under GPL (Open Source) License

- MPL provided with SoC EDS as an example using the HWLibs (Altera bare-metal libraries). Uses BSD license.

Note: The Preloader requires a special header to be placed at the beginning of the next stage boot image. Also, the header contains a CRC value used to validate the image. The header can be attached to an image by using the mkimage utility that is included with the SoC EDS.

#### Bootloader

The Bootloader has typical responsibilities that are similar with the Preloader, except it does not need to bring up SDRAM.

Because the Bootloader is already residing in SDRAM, it is not limited by the size of the OCRAM. Therefore, it can provide a lot of features, such as network stack support.