## Hi all,

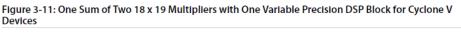

I am optimizing a filter that was made in a Cyclone V device. The current filter uses two DSP blocks for two multiplications; according to the Cyclone V device handbook, it should be possible to fit two independent multipliers in one DSP block. I tried to implement the multipliers by using the 'Multiply adder' intel FPGA which uses the 'altera\_mult\_add' module from the 'altera\_lm' library. Unfortunately, it seems to implement the two multipliers in 'Multiplier Adder mode', this mode is shown in the figure below.

## Multiplier Adder Sum Mode

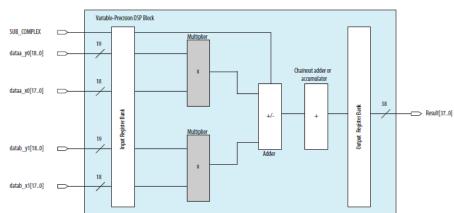

I would like to implement the two multipliers independently. However, I can't figure out how I can bypass the adder from the DSP block as shown in the next figure.

I would be very thankful if someone can give me a solution to this problem, I am working with the Intel FPGA lite 18.1 software.

Kind regards,

Bas van Wijngaarden