I’ve said it before, and I’ll say it again -- today’s computational workloads are larger, more complex, and more diverse than ever before. The explosion of applications like high-performance computing (HPC), artificial intelligence (AI), machine vision, analytics, and other specialized tasks is driving the exponential growth of data.

Processing this data requires humongous amounts of computational power. Many of these data processing tasks can be dramatically speeded if implemented in a massively parallel fashion using the programmable fabric inside an FPGA. A common way to implement this hardware acceleration is to augment the X86 CPU-based motherboard in a workstation or server with an FPGA-based acceleration card connected via a PCIe interface. Examples of such cards are the IA-420F (low-profile) and the IA-840F (double-width) accelerator cards from BittWare, both of which are powered by Intel Agilex F-Series FPGAs.

A major consideration is to convey the source data from the host computer to the FPGA for processing, and to return the result data from the FPGA back to the host at the highest possible speed. Many new socket opportunities require PCIe Gen4 x16 throughput between the host and the FPGA. Intel Agilex F-Series FPGAs support PCIe Gen4 x16 with a theoretical bandwidth of up to 220 Gpbs, but traditional interrupt-driven processing on the host side makes it impossible to achieve this bandwidth.

In order to access the maximum bandwidth possible, one part of the solution is provided by the Data Plane Development Kit (DPDK), which is an open-source software project managed by the Linux Foundation. The DPDK provides a set of data plane libraries and network interface controller polling-mode drivers for offloading TCP packet processing from the operating system kernel to processes running in user space. This offloading can achieve higher computing efficiency and higher packet throughput than is possible using the interrupt-driven processing provided in the kernel.

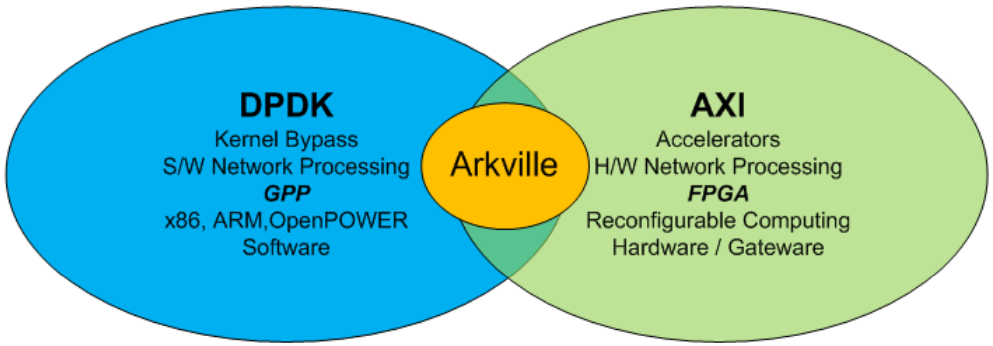

Another part of the solution is the Arkville DPDK IP Core from Atomic Rules. This “data mover” core, which is implemented in the FPGA, provides a high throughput line-rate agnostic conduit between the general-purpose processor (GPP) software on the host and the FPGA hardware on the accelerator card using industry-standard DPDK interfaces on the software API/ABI side and AXI interfaces on the FPGA side.

Arkville provides a DPDK packet conduit (Image source: Atomic Rules)

The Arkville DPDK IP Core was recently updated (rev. 21.11) to support Intel Agilex FPGAs, including those powering BittWare’s latest IA-series of products. The Arkville core moves data at up to 220 Gbps over PCIe Gen4 x16.

All of this will be discussed in detail in the Arkville PCIe Gen4 Data Mover Using Intel® Agilex™ FPGAs Webinar, which will be held on Tuesday 14 Dec 2021 @11:00 am EST. In this webinar you’ll hear from Jeff Milrod at BittWare who will be introducing products supporting Intel Agilex FPGAs and the use of data mover IP in a variety of markets. Tom Schulte from Intel will provide perspective on the Agilex product line, including future features such as PCIe Gen5 x16 support. The webinar will conclude with Shep Siegel from Atomic Rules who will give a demo and explain the performance achieved with the Arkville data mover IP on Agilex FPGAs. Shep will also provide insight into how Arkville reduces time-to-market and makes development easier without sacrificing performance.

Register today to gain access to this event, including a live Q&A session with our presenters. As part of this, you will also have the ability to watch the recording of the webinar on demand.

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.