- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

On our custom hardware, when pulling down pin 28 (DEV_OFF) the i210 network controller is still operational. Means ethernet communication is still possible. I expected the controller will power down the PHY, but nothing happens. I measured directly at the pin. We have a clean low level there.

It seems like the state of DEV_OFF is completely ignored by i210.

Yes, we enabled the DEV_OFF_N pin via Bit 15 = 1 in Flash-Word 0x1E.

The whole register content is set to 0xb200.

Are there any additional conditions to be fullfilled to enter "device off mode"?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @AMart139:

Thank you for contacting Intel Embedded Community.

Could you please let us know how many units of the project related to this circumstance have been manufactured? How many are affected? Could you please give the failure rate? Also, could you please list the sources that you have used to design it and if it has been verified by Intel?

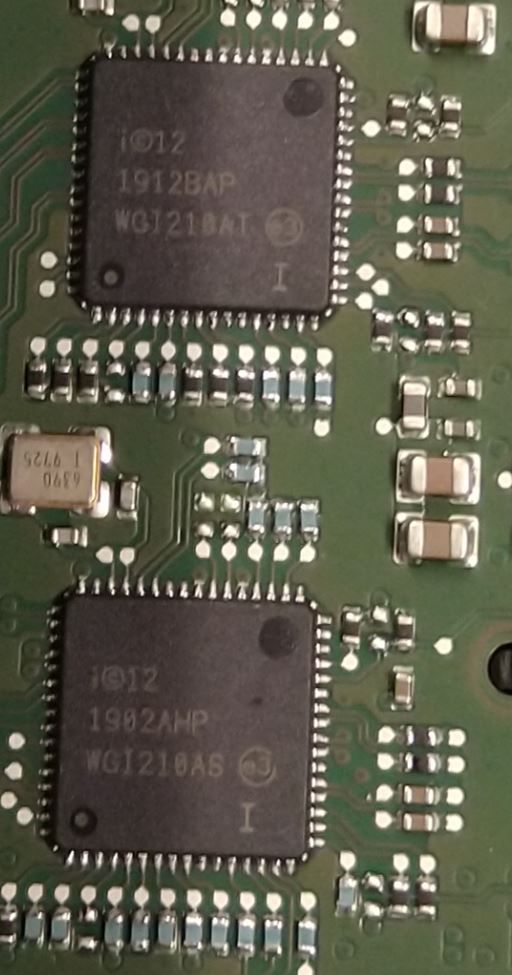

Finally, could you please give pictures of the top side markings of the affected Ethernet Controllers? Because the attached one does not have clear this information.

We are waiting for your answer to these questions.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are currently in development phase. Thus only a few units (~50) have been manufactured for prototyping. Our design is based on Intels reference design and has not been verified by intel.

It doesn't necessarily have to be an issue on i210 side. I assume there are additional conditions that have to be fullfilled to enter der device off mode. That's reason why I'm asking.

It could also be that the chip enters the mode, but immediately leaves it again due to another event (possibly PCIc triggered). Is this possible?

Are there some known erratas in this context?

See picture of top side markings attached.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, @AMart139:

Thanks for your updates.

Could you please verify that the affected implementations fulfills the configuration requirements stated in Table 2-11, on page 30 of the Intel(R) Ethernet Controller I210 Datasheet document # 333016? This document can be found at:

On the other hand, in case that you want to request a full verification of your schematics or layout implementation, please follow the procedure stated in the following website:

https://edc.intel.com/Tools/Design-Review/Default.aspx

We are waiting for your answer to this communication.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@AMart139: There is probably nothing wrong with your schematics. The reason controller seems to ignore DEV_OFF pin is that the pin level alone is not sufficient to disable controller. There is also NVM Device Off Enable bit that you need to set. Refer to Table 2-9 , Section 2.4 of the i210 controller datasheet, document 335761, link is in this message thread..

Good luck!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page