- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,I want to add veb/vepa and vsi through commands on the pv of xl710.But i am having some problems adding veb and vsi.

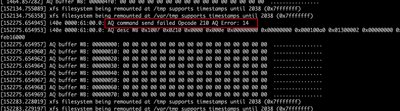

I can correctly add floating VEBs. But an error occurred while adding VEB with uplink and downlink.Appear “AQ command send failed Opcode 230 AQ Error:14 AQ desc WB 0x0007 0x0230 0x0000 0x000e 0x00000000 0x00000000 0x01860002 0x00ff0003 0x00000000 0x000b0000”

Secondly I also got error while adding vsi.

I put more detailed information in the attachment.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @migo_gong,

Thank you for contacting Intel Embedded Community.

Could you please clarify if this request is related to the Intel® Ethernet Controller XL710 design developed by you, or is a Network Interface Card (NIC) or add-in card developed by a third-party company?

Could you please let us know the name of the manufacturer, the part number, and where we can find the information on this device if it is a third-party design?

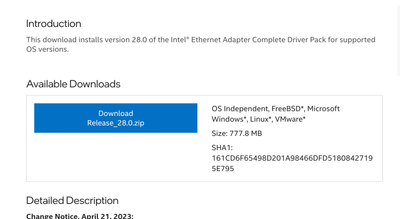

Can you check the most recent drivers for the Intel® Ethernet Controller XL710:

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for your response.

I am a student of network engineering, currently learning to use the features of xl710. While working with it, I came up with a simple idea to create a graphical interface in Linux. I have reviewed the data manual and the i40e code, but I haven't been able to utilize the basic functionalities yet. The main difficulty lies in the issue I mentioned in the attachment. This problem has been bothering me for a while, and I haven't been able to solve it. Therefore, I would like to seek the guidance of an Intel professional engineer.

I sincerely hope that you can help me resolve this issue, and I truly appreciate your assistance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, if you see this, could you please reply?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @migo_gong,

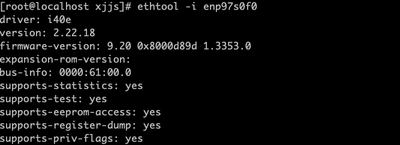

My apologies, I had this pending but being busy, I think the issue might be in incompatibility from driver and firmware, you can try to update the firmware of the controller to the latest and use the latest driver and then try again.

You may check this document for compatibilities between driver and firmware versions:

Driver i40e. I think you are using igb, is okay but the version should match the document of compatibilities.

You can try to update the NVM with this document but you must be very careful.

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, the firmware update download page I found is shown in Image1, but you provided Image 2. Is there any difference between these two?

I should update which one?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @migo_gong,

I have shared you the one of ~700 Mb, include many images, use the one of your controller:

"You can try to update the NVM with this document but you must be very careful.

What is the second one from?

Also, you can use this as a tutorial:

Intel® Ethernet NVM Update Tool Quick Usage Guide for Linux

Best regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"Thank you for taking the time to reply. :

I have already updated to the latest version.

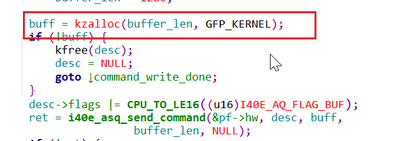

Below is the command code I entered and the error feedback received.

(1)code

(2)Error feedback:

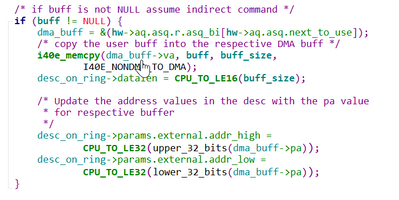

My driver version is the latest 2.22.18. However, while examining the command issuing process, I noticed that the driver does not handle the high and low addresses provided in my command. Can you confirm if the address of the command buffer provided in section 7.4.9.5.5.1 of the datasheet for the 'add vsi' command is the address that needs to be provided in the command? If it is, where does the driver handle it? I haven't seen any relevant processing except for the initial allocation of a buffer with a specified length (buff), but buff is not the address I provided for the command buffer. Moreover, the driver still sends this empty buff to the DMA."

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page