- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

18.0.1 Pro & Stratix 10

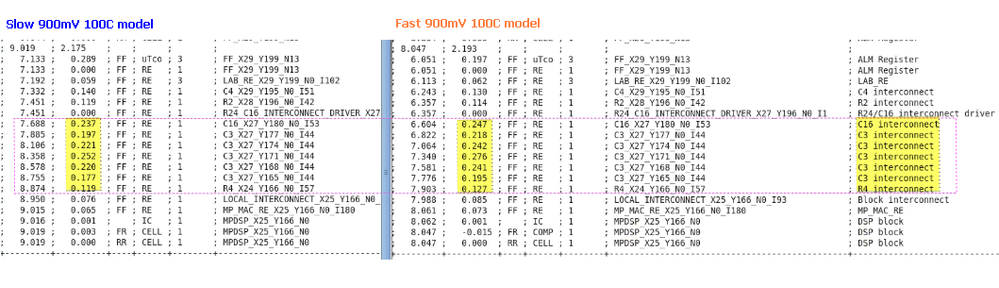

One of my failed setup timing path has larger -ve slack in Fast Corner than Slow Corner. When look deeper, I noticed the C3 interconnect delay in fast corner is much larger than in slow corner as shown in the attached diagram. Any idea ?

Thanks

- Tags:

- timing

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi gNATO!

I can't see all the diagram, and to answer your question it is an addititional information need to be added.

You can see that it is not only C3 interconnect that is larger for a Fast Corner, also practically all delays are larger (LAB RE, C4 inerconnect, R2 interconnect and so on).

For now I can say that maybe it is an effect called late derating in On-Chip Variation mode of analysis.

It can be even Stage-based OCV, where some part of path can behave in another way as it should be expected.

--

Best regards,

Ivan

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page