- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

we are using Arria10 GX device, and we are using CPRI IP v7.0 in our project.

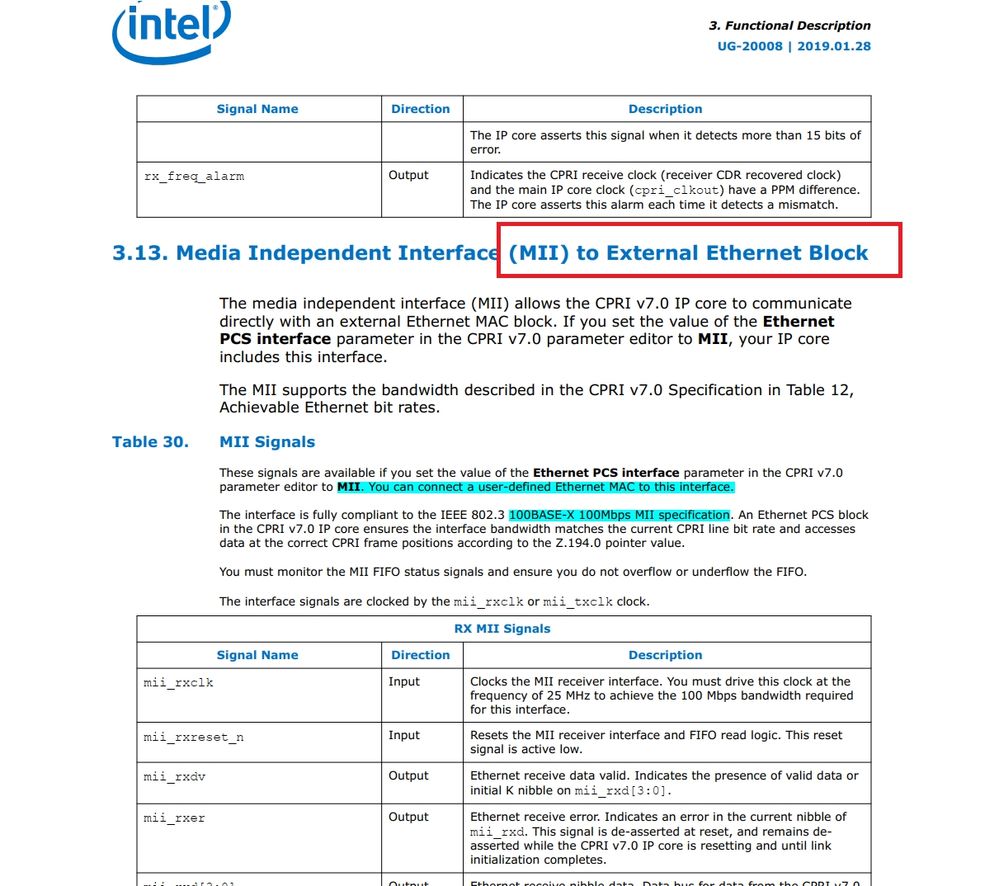

CPRI DATA Path has been verified OK, and the next step we wantsto verify is cpri "C&M" Path, which according to Intel CPRi IP user guide, we could use 【 Media Independent Interface (MII)

】 I guess. But the problem is we don't know HOW TO USE this MII interface.

Q1: in my opinion, CPRI MII i/f is enabed by configuring several cpri parameters, But I think CPRI MII block is a PHY-alike componet , so what is the FPGA MAC IP should be selected ?

Do we need instantiate a FPGA MAC IP , and connect to the CPRI MII interface, correct ?

2 if this is the case, since our Host is Linux OS, where can we find reference Linux Driver for this “ FPGA MAC - CPRI PHY” (on PCIE Bus) ?

This is urge, thus pls help to advise.

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, you have some inquiries related to the MII interface of the CPRI IP. For your information, this interface is fully compliant to the IEEE 802.3 100BASE-X 100Mbps MII specification. The CPRI IP include the Ethernet PCS block. You would need to code or add the other layers ie MAC to interface with the MII interface.

As I understand it from the user guide, the IP generated example design have simulation which demonstrate some transaction to MII interface. You may refer to the "Understanding the Testbench" section in the CPRI user guide for further details.

Regarding your inquiry on the reference Linux driver, sorry as I do not have any insight on this and could not comment on it. Sorry for the inconvenience.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks CheePin for reply,

So according to your suggestion, a general usage of CPRI Mii interface is " customer need to instantiate a 100M Ethernt MAC IP, and connect it to that cpri mii signal interface ". thus the Host driver would communicate with the FPGA MAC IP to treat it as a standard “ethernet device", correct ?

Then I may have raise a new question:

1) our FPGA card use PCIe link inside Host Machine, From host point of view, it's a PCIe EP, and it works as a CPRI FH Card for IQ transmit & Receiving.

2) If we enable CPRI MII i/f, and connect it to a FPGA internal MAC IP. In my opinion, we need expose it as a "standard" ethernet device point in Host Linux World (such as, “eth1” alike), thus we can operate it alike standard ETHERNET PORT.

MY Wonder : does it mean the single FPGA PCIE card should implement the multi-function Endpoint functionlity ( one is CPRI IQ DATA tx&rx function; and another is a *standard* ETEHRNET fucntion), so Host OS can load seperate drivers for them one by one ?

is it correct ? DOes ARRIA10 support "a multi-function Endpoint" usage case ? Thanks in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For the CPRI MII interface, it is an Ethernet interface. However, since I am not an Ethernet expert, I could not comment which specific Ethernet IP to use. As long as the interface comply with MII specs, then it should be fine.

Regarding your latest inquiries related to the PCIe endpoints, it would be great if you could help to open a new case so that our PCIe expert could further assist. You may let me know the case after created, I can help to notifiy the PCIe team to expedite the routing.

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As I understand it, it has been some time since I last heard from you. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page