- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please tell me about word boundary and bit order of ALTLVDS_TX.

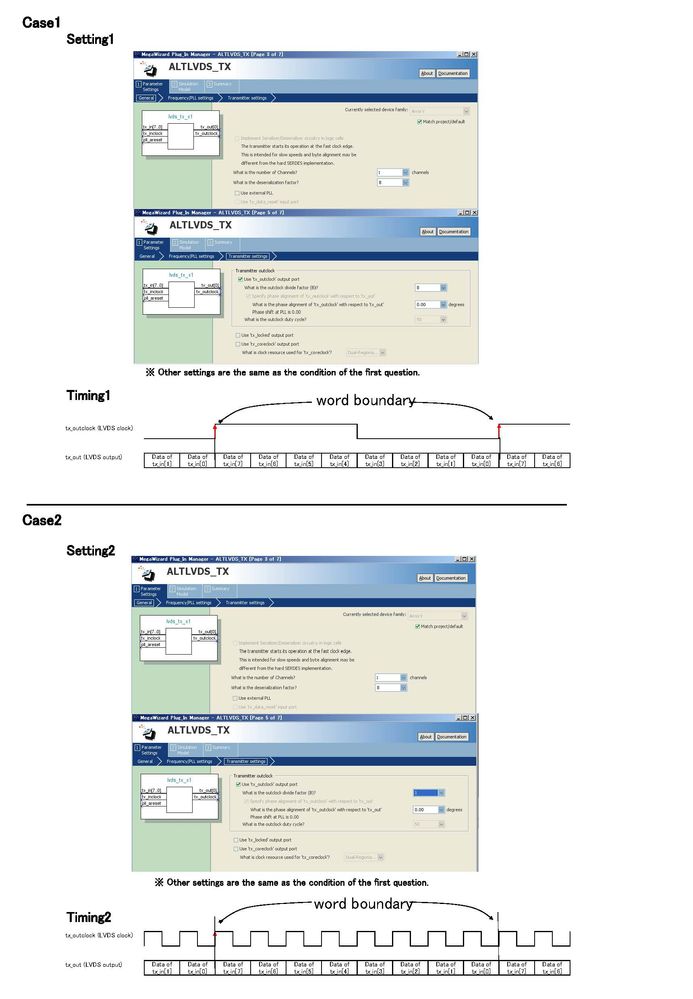

In the simple "condition" as shown below, can you think that the word boundary and the bit order of ALTLVDS_TX become like the following ① and ②?

* I would like to know about the word boundary and the bit order when not considering delays such as placement and routing.

① The rising timing of tx_outclock becomes the word boundary of tx_out.

② In addition, considering the word boundary as a reference, data output order of tx_out is output in the following order.

Data of tx_in [0] → Data of tx_in [1] → · · · tx_in [7] data

------------------

ALTLVDS_TXのワード境界とビットオーダーについて教えてください。

下記のようなシンプルな「条件」において、ALTLVDS_TXのワード境界とビットオーダーは下記①と②のようになると考えて良いでしょうか。

※配置配線等の遅延を考慮しない場合のワード境界とビットオーダーについて知りたいです。

①tx_outclockの立ち上がりタイミングが、tx_outのワード境界になる。

②また、そのワード境界を基準に考えると、tx_outのデータ出力順序は、下記の順序でデータ出力される。

tx_in[0]のデータ → tx_in[1]のデータ → ・・・ tx_in[7]のデータ

--------------

条件(condition)

--------------

■環境

・TOOL Quartus Prime v16.0

・FAMILY "Arria V"

・DEVICE 5AGXFB3H4F35C4

■ALTLVDS_TXの設定

[General]

What is the number of Channels? 1 channels

What is the deserialization factor? 8

Use external PLL: "No Check"

[Frequency/PLL settings]

What is the output data rate? 200.0 Mbps

Specify input clock rate by clock frequency 25.000000 MHz

What is the phase alignment of 'tx_in' with respect to the rising edge of 'tx_inclock'? 0.00 degree

Use "pll_areset' input port: "Check"

Register 'tx_in' input port using: tx_coreclock

[Transmitter Setting]

Use 'tx_outclock' output port: 1

What is the phase alignment of 'tx_outclock' with respect to 'tx_out': 0.00 degree

この設定で生成されるポート

tx_in[7..0] データ入力

tx_inclock クロック入力

pll_areset 非同期リセット入力

tx_out LVDS外部出力へピンアサイン

tx_outclock LVDS外部出力へピンアサイン

※各信号は、デバイスの規定通りピンにアサイン出来ているものとします。

--------------

参考にした資料

--------------

下記資料のFigure 6-36: Bit-Order and Word Boundary for One Differential Channel

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-v/av_5v2.pdf#page=222

下記資料36ページ「図3-5-1-3シリアライザの動作イメージ」のように、tx_outclockとデータ(d6..d0)との関係を知りたいです。

https://www.altima.jp/members/pdf/CyloneIV_LVDS_TX_design_v12_r1.pdf#page=36

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Swap timing 1 and timing 2.

When you set B = 8, you should have divided to 8 clock cycles for 8 bits.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Songokuu

Just to make sure that I understand you correctly, your question is which is correct, MSB first or LSB first in the serial data, right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ご返信ありがとうございます。

はい。補足しますと、質問②については、ALTLVDS_TXのtx_out信号(LVDS出力)は、tx_in信号のLSBから先に出力されるかを確認したいです。

また、ご質問は①②の2つあります。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Songokuu

① The rising timing of tx_outclock becomes the word boundary of tx_out.

1) Yes, tx_outclock is the tx_out boundary when outclock divide factor (B) = 1

② In addition, considering the word boundary as a reference, data output order of tx_out is output in the following order.

2) If I recall correctly, the interface always sends the most significant bit (MSB) of your parallel data first.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ご返信有難う御座います。理解が深まりました。

>① The rising timing of tx_outclock becomes the word boundary of tx_out.

>1) Yes, tx_outclock is the tx_out boundary when outclock divide factor (B) = 1

>

→追加で確認させてください。

「What is the outclock divide factor (B) = 8」の時は、tx_outclockの"立ち上がりタイミング"が、tx_outのワード境界になるのでしょうか。

※その他の設定は、最初のご質問の条件(condition)と同様とします。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ご返信ありがとうございます。

整理すると、下記の理解で正しいでしょうか。

(File Name : 20190314_TimingChart_and_Setting.jpg)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Swap timing 1 and timing 2.

When you set B = 8, you should have divided to 8 clock cycles for 8 bits.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page