- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey,

I have burned .sof(The FPGA program) and .hex (some parametrs that I have been created) files into the configuration flash (via JIC file).

my FPGA program uses the Generic Serial Flash IP and I'm trying to read the .hex file parameters but I can't assign the Configuration Flash's pins into the the FPGA design. I got the error "Value entered is not a valid location".

I would like to get some help here'

Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Are you using the Generic Serial Flash Interface IP?

If that is the case, you do not need to manually assign the pins: just leave unchecked the parameters about the ASMI interface and QSPI pins (I don't remember how they are exactly called). Quartus is going to automatically connect the IP to the Active Serial Configuration pins (check the compilation report to be sure).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yeah, I'm using this IP.

How can I use those Altera's reserved pins after the configuration process(in User mode) ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

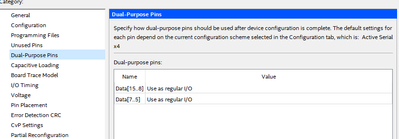

Then in "configuration," make sur you have selected "active serial" (or "active serial x4"). In "dual purpose pins", put everything to "user i/o".

Then you will be able to use those pins in user mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I see only the Data[15...8] and Data[7...0] in the "dual purpose pins" tab :

I don't see the Flash pins such as Dclk, ncs AS Data[3...0]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ah yes you're right.

I assumed that, based on the message at the top of the window, Quartus was automatically refering to the configuration pins for the selected configuration mode.

So either the AS pins are available by default as user I/Os in User mode, or the setting for this behaviour is elsewhere...

However I do not know of other settings about this. In a design, I use the AS configuration pins as user I/Os to access a QSPI flash (just as you do) and it works. Only thing is that I program the FPGA with JTAG (.sof file) and not actual active serial, despite the Quartus settings.

Is it possible for you to try?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Quick note: I stumbled on a "Enable input tri-state on active configuration pins in user mode" option in "Device&pins options"' configuration page. It is disabled by default and I have never changed it.

Maybe you can use this to prevent user access to AS pins?

By the way I use Arria 10 SOC (I do not know if it is relevant here)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page