- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I was referring to AN778 https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an778.pdf

I was checking the guidelines regarding bonded mode (x2) using GXT channels. I am using Stratix 10 SX SoC dev kit which has L-tile transceiver. In AN778, there is a chapter "2.1.2.2. Bonded GX Channels ". However, there is no information for Bonding the GXT transceivers.

I am aware of GXT lanes are not continuous (i.e. ch0,1, 3 and 4 can be GXT channels in bank 1 and 3). With this only x2 bonding is possible (considering the channel number continuity). I want to know whether x2 bonding is allowed in GXT transceivers or bonding option is not available for L-tile GXT transceivers.

With Regards,

HPB

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @NathanR_Intel ,

Yes, That was my specific question. 3.3.4 of user guide says the ATX PLL can drive the no. of non-bonded channels. But, I did't find any statement in the S-10 XCVR PHY user guide which states that L-tile XCVRs doesn't support bonding mode. If I configure XCVR L-tile native PHY in the platform designer tool with Bonded mode for GXT, I am not seeing any error message (for S-10 SoC dev kit) saying that Bonded mode is not supported for L-tile XCVRs. As I am possessing incomplete information regarding XCVR PHY bonded mode support, I am looking for a document support explicitly describing the Bonded mode is supported or L-Tile native PHY in S-10.

With regards,

HPB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @NathanR_Intel ,

As I know, Channel Bonding is the feature of PCS. I want to write a custom PCS, then whether I can write a custom logic to take care channel Bonding? What are the dependencies of channel bonding wrt PMA block?

With regards,

HPB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @NathanR_Intel ,

https://www.youtube.com/watch?v=PxAx_xR_iJA

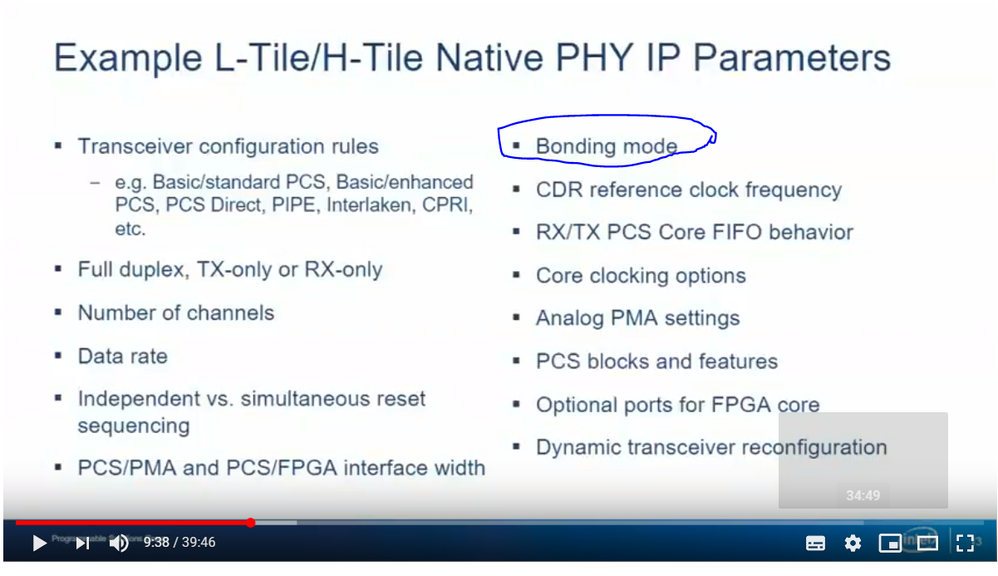

In this training video "Building an Intel® Stratix® 10 FPGA Transceiver PHY Layer", the material says that Bonding mode can be configured for L tile / H-tile XCVR PHY.

With Regards,

HPB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nathan,

"This could be because you data rate is lower allowing Quartus Prime Pro to used x6 or x24 clock line. If your data rate is higher than 17.4Gbps, then this is because the Native Phy IP System Messages does not error this out. You will need to perform full compilation to observe error in fitter."

You are right. I get the error while configuring the ATX PLL with master CGB

Also, I am seeing same behaviour for an H-tile device also.

I think even H-tile transceiver doesn't support x2 bonded mode for more than 17Gbps.

The reason being, I created the project for H-tile S-10 FPGA (1SX280HUF50E1...) and in the platform designer I am getting the error " Master CGB input clock frequency (9667.96875MHz) is above maximum allowed (8700MHz).

So, my conclusion is either L-tile or H-tile XCVR doesn't support x2 bonded mode for more than 17Gbps link rate.

With Regards,

HPB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have some ~20ns skew tolerance between 2 channels. I want to know what would be the data skew between 2 adjacent TX channels (PMA skew).

With regards,

HPB

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page