- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

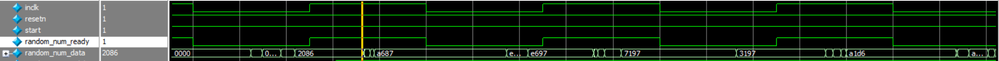

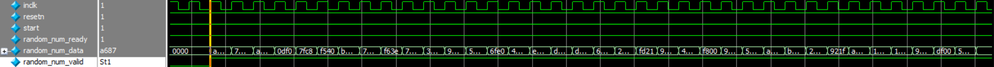

Simulate the Random Number Generator IP Core with ModelSim. The same testbench, when choosing different devices, the simulation results of rand_num_data are quite different.

(1) When stratix iv (EP4SGX230KF40I3) is selected, rand_num_data is not synchronized with inclk. And when the clock frequency is increased to 320MHz, rand_num_data will have an indeterminate state Z.

(2) When Arria 10 (10AX027H4F34I3SG) is selected, rand_num_data is synchronized with inclk. And when the clock frequency is increased to 320MHz, rand_num_data is still output normally.

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

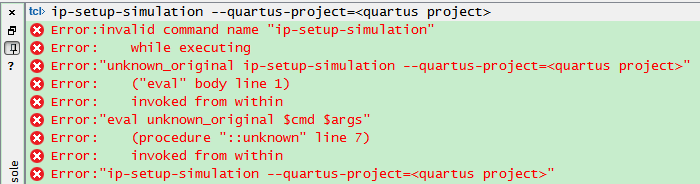

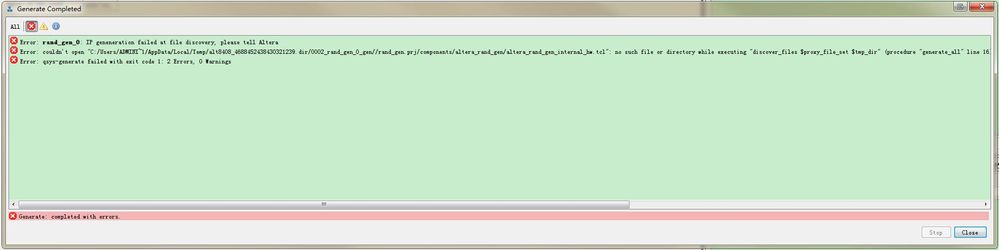

Continuing the previous reply, I added a figure about the errors of tcl console.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Regarding your observation where when increasing the frequency of the clock for SIV rand generator IP simulation, the simulation seems to have issue. For your information, I am able to replicate similar observation when increasing the frequency from 100MHz to 200MHz. I believe this is due to limitation of the simulation model at high frequency. However, in actual hardware implementation, the core performance should be limited your timing closure. As a workaround, you can simulate the functionality at 100MHz and then implement the actual frequency in your design.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I will implement in my actual hardware.

Thanks very much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Regarding the test bench template writer, for your information, I do not have much insight into it. Generally I would code the test bench from scratch or use the example design generated by the IP. However, for the SIV rand IP, seems like there is no example design generation supported. Sorry for the inconvenience. As a workaround, I would like to recommend you to code your test bench in RTL.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I will do as you recommended.

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks lot for your help and update.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

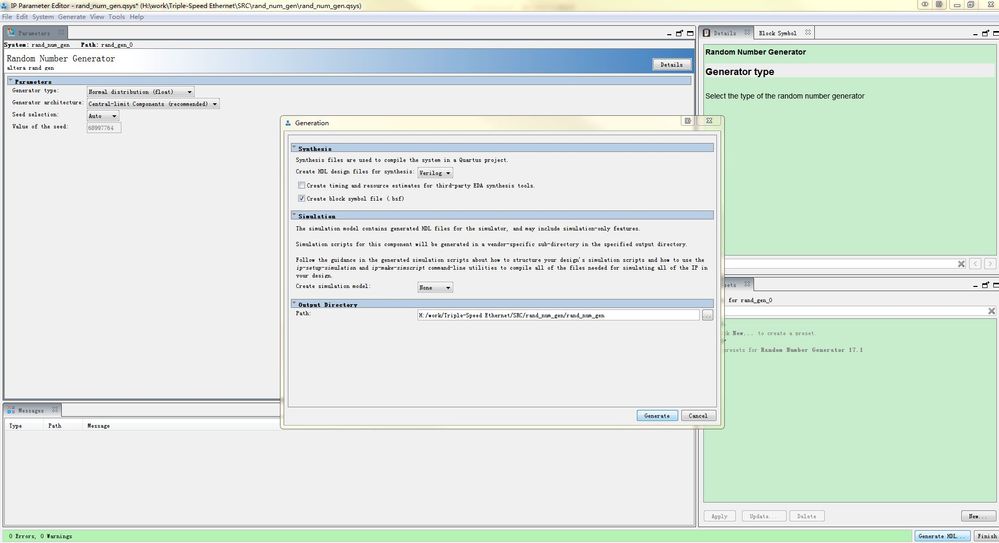

I ran into a difficult problem. When using the 17.1 standard version to create a random number IP, an error will be reported, see the text and the attachments.

I am very anxious and look forward to your reply, thank you.

Error: couldn't open "C:/Users/ADMINI~1/AppData/Local/Temp/alt8408_4688452438430321239.dir/0002_rand_gen_0_gen//rand_gen.prj/components/altera_rand_gen/altera_rand_gen_internal_hw.tcl": no such file or directory

while executing

"discover_files $proxy_file_set $tmp_dir"

(procedure "generate_all" line 16)

invoked from within

"generate_all $output_name QUARTUS_SYNTH"

(procedure "generate_quartus_synth" line 2)

invoked from within

"generate_quartus_synth rand_num_gen_rand_gen_0"

Error: qsys-generate failed with exit code 1: 2 Errors, 0 Warnings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »