- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

When synthesis design for AGIB027R31B1E1VAA that contains F-Tile Ethernet Intel FPGA on Intel Agilex ® 7 FPGA I-Series Transceiver-SoC Development Kit I got the next error:

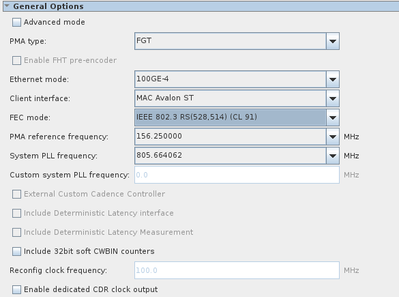

The specified block fm87_top_bd|mac_subsystem_0|mac_100g|eth_f_0|hip_inst|per_xcvr[0].x_bb_f_ux|x_bb_f_ux_rx cannot be placed at the location fgt_q2_ch0_rx as the block requires stream(s) [0] in an Ethernet 100g block but the location only supports stream(s) [1, 2, 3].Transceivers pins are connected to QSFPDD0 connector. I have the same error for QSFPDD1 connector. IP settings are shown below. Pins assignments were taken from design example in agilex_agib027r31b1e1vaa_si_en_revb_v23.1b115_v1.0.zip archive.

F-Tile Reference and System PLL Clock Intel® FPGA IP settings:

Can you tell me what I did wrong?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi redst,

I think you might use the wrong Quad in this case. You are suggested to use the f-tile-channel-placement tool before do the pin assignment for the Quad. Different topology will show different available Quad.

Best regards,

Zi Ying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi redst,

You can get the F tile Channel Placement Tool in link below, Section 7.1, pg 231, https://www.intel.com/content/www/us/en/docs/programmable/683872/23-1-4-4-0/f-tile-channel-placement-tool.html

Best regards,

Zi Ying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank your for your answers.

To be honest I didn't understand how to use F tile Channel Placement Tool in my case. I tried Quartus tool Tile Interface Planner and found out that when I assign pin to a specific location the tool assigns the rest of locations automatically.

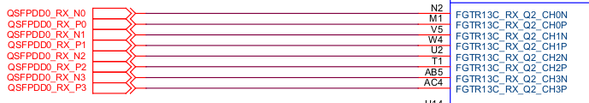

In my case it looked like this.

I want to use QSFPDD0 socket so I looked into schematic and found out what pin numbers I should use:

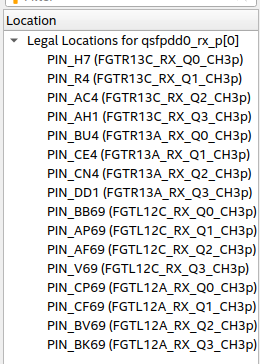

Then I go to Tile Interface Planner and in "Plan design" bookmark I see that input signal of my design qsfpdd_rx_p[0] has the next options for placement:

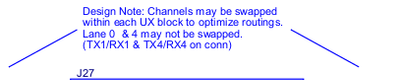

I don't see here the right pin number. But In the same file with schematic i can see such note:

Anyways I see that pin's location of QSFPDD_RX_P0 M1 is in list for qsfpdd_rx_p[3] so it seems they are really swapped.

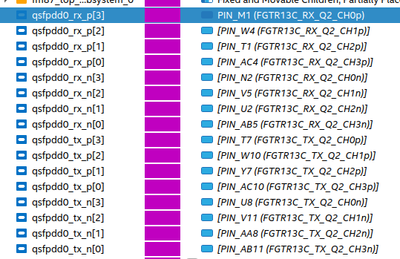

Then I choose M1 location for qsfpdd_rx_p[3] and as a result all the rest of locations are mapped automatically:

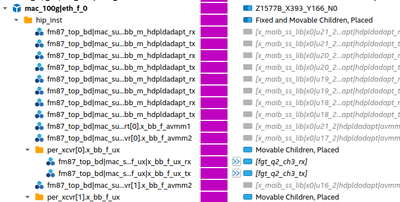

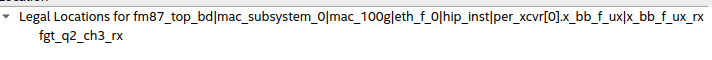

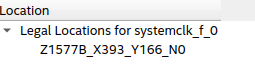

And the Ethernet hard IP now has its location set to:

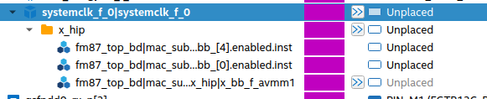

And the problem here that I cant move transceivers to another quad as they have only one location option:

The same with reference clk pll. The tool allows me to choose location:

But there is only one option

So in the end after I did all these assignments assembling passes with no errors. But now I'm not sure whether it will work with those swapped pins or not.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Would you mind to share your .qar file? So that I can try debug issue from my side.

Best regards,

Zi Ying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I will try to create a demo project.

But right now I'm facing a problem as I don't see the link is up after programming the device.

During compilation I got this kind of messages appearing:

Critical Warning(23469): The block fm87_top_bd|mac_subsystem_0|eth_mac|eth_f_0|hip_inst|per_xcvr[0].x_bb_f_ux|x_bb_f_ux_tx did not set the following parameters

Critical Warning(23469): The block fm87_top_bd|mac_subsystem_0|eth_mac|eth_f_0|hip_inst|per_xcvr[1].x_bb_f_ux|x_bb_f_ux_tx did not set the following parameters

Critical Warning(23469): The block fm87_top_bd|mac_subsystem_0|eth_mac|eth_f_0|hip_inst|per_xcvr[2].x_bb_f_ux|x_bb_f_ux_tx did not set the following parameters

Critical Warning(23469): The block fm87_top_bd|mac_subsystem_0|eth_mac|eth_f_0|hip_inst|per_xcvr[3].x_bb_f_ux|x_bb_f_ux_tx did not set the following parameters

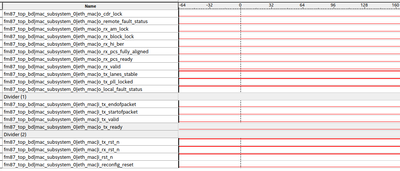

Also using signal tap I could see what was going on on status pins of the ethernet IP:

Also i have the next state of QSFPDD control signals:

qsfpdd0_resetl = 1'b1;

qsfpdd0_modsell = 1'b0;

qsfpdd0_lpmode = 1'b1;

Right now I have no idea of what can be wrong and what can I do to bring the link up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

I have an update. It seems I could establish the link. I've changed cable I used, assigned all HIP from the scratch and the link got up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Great to hear you that you establish the link successfully. Since your issue has been resolved, I am now close the case. If you have any question after the case close, please do feel free to submit another issue.

Best regards,

Zi Ying

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page