- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi guys,

I am trying to compile the Example Design for Multichannel DMA PCIe IPCore. However the placement stage failed and the following error has been reported.

The issue appeared when I initially choose the partnumber 1SG040HH3F35E3VG.

On the other hand I can successfully compile with 1SG065HH3F35E3VG partnumber.

Error message:

Info(175028): The pin name(s): pcie_rstn_pin_perst

Error(175006): There is no routing connectivity between the pin and destination HSSI_CR2_PHIP2_CORE

Info(175027): Destination: HSSI_CR2_PHIP2_CORE dut|dut|hip|altera_pcie_s10_hip_ast_pipen1b_inst|wys

Error(175022): The pin could not be placed in any location to satisfy its connectivity requirements

Info(175021): The HSSI_CR2_PHIP2_CORE was placed in location HSSICR2PHIP2CORE_5TL0

Regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can I know which quartus version you running the example on ?

Is it running in Window or Linux version ?

Hoping to hear back from you

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I am using

Quartus Prime Design Software

Version 22.2.0 Build 94 06/08/2022 SC Pro Edition

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is Linux Suse (Enterprise Version)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For Error 175006 :

You may see this error in the Intel® Quartus® Prime Pro software when using LVDS SERDES Intel FPGA IP with Intel Stratix® 10 devices.

This error occurs when the input clock signal of the IOPLL is being sourced through the FPGA core.

To avoid this error, provide the input clock signal to the IOPLL through dedicated clock pins.

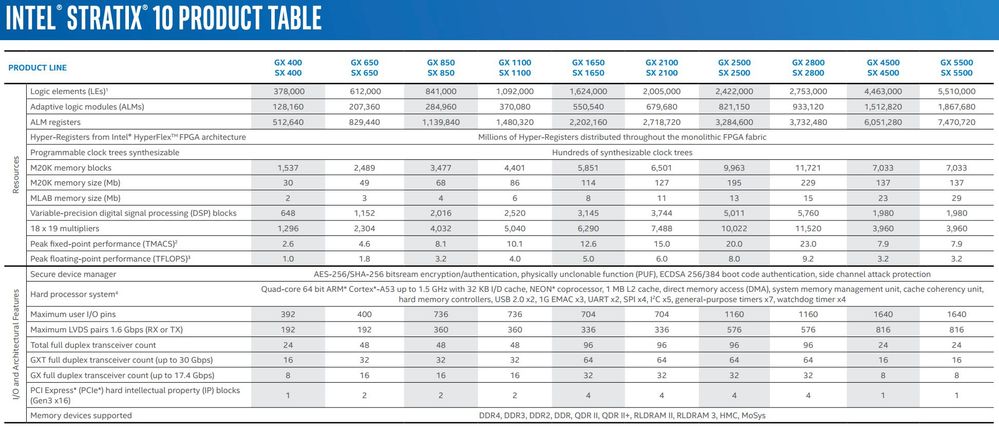

Stratix 10 support PCIe Gen3x16 from lane 1-4 , can you please check the table below and ensure that the configuration is correct ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

1) Regarding to LVDS SERDES,

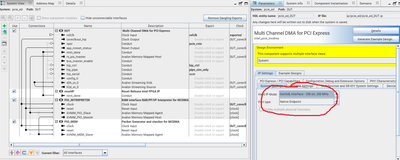

I have successfully synthesized the same project for 1SG065HH3F35E3VG device and back-annoted the voltage pattern, as you can see below.

set_instance_assignment -name IO_STANDARD "HIGH SPEED DIFFERENTIAL I/O" -to xcvr_tx_out*

set_instance_assignment -name IO_STANDARD "CURRENT MODE LOGIC (CML)" -to xcvr_rx_in*

Then I constrained the project for 1SG040HH3F35E3VG using the same IO Standard and I have gotten the same issue.

2) Regarding to IOPLL,

after yout last message I have tried to constraint only the pins xcvr_rx/tx, perst and refclk. I assume that the correct pin to conect refclk is PIN_AC28 according to the 1SG040_HF35 pin list provided by Intel (attached the QSF)

3) Regarding to PCIe Gen3x16 from lane 1-4, I am trying to use PCIe Gen3x8 with 1SG040HH3F35E3VG. I am not sure which configuration you have suggested to check.

Since it is successfully compiling for 1SG065 with no pinning constraint, shouldn't it compile for 1SG040 as well?

Regards,

Arley

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arley,

Glad that the error not appear, please proceed with 1SG040 as well.

Looking forward to hear back from you.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I didn't mean that the error didn't appear with 1SG040. Probably I wasn't clear, sorry. In my last message I described all my unsuccessfully trials with this device (040) and I also have tried the same project with another device (065) which is pin to pin compatible.

Regards,

Arley

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arley,

My fault, I misunderstood your last message.

Is it possible to provide .qar file so that I can take a look at the design?

For the support ticket, can please provide me the ticket number so that I can take a look on it ?

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arley,

In the mean time, please try following this support answer to see if it resolves your error:

https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/hsio/2019/error-18969---io-banks---1c-1d-1e-1f----are-within-same-hssi-str.html

Hoping to hear back from you.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Following a Intel brazilian suggestion I have opened a new support request with my company email.

https://supporttickets.intel.com/requestdetail?id=5004U00000z4Y0HQAU&lang=en-US

If you want I can update here the support progress.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

The request number of the support ticket is 05595818

Please let me know if you get problem to see the .qar file.

Regards,

Arley

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Arley,

As it is exactly the same question. Please allow me to have some time to take a look at the .qar file

This thread will be close as duplicate and transitioned to community support.

I will continue to support you in the new thread.

In this case, the community users will continue to help you on this thread.

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or please let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page