- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello everyone,

I'm successfully using the Generic Serial Flash Interface (GSFI) to write/read from a MT25QL256 flash in Quad mode, 4-byte addressing (1-4-4 protocol).

The firmware bootcopier also use it successfully and I'm able to load the FW in RAM at power up. I'm using the default bootcopier from Intel (boot_loader_cfi.srec).

I followed this very useful example to configure the GSFI: https://community.intel.com/t5/FPGA-Wiki/Generic-Serial-Flash-Interface-GSFI-and-Nios-II-Booting-Quick/ta-p/1201053

The only issue happen in the firmware for user data read/write: I need to manually poll the flash Flag Status Register to know when the flash is busy during a write operation!

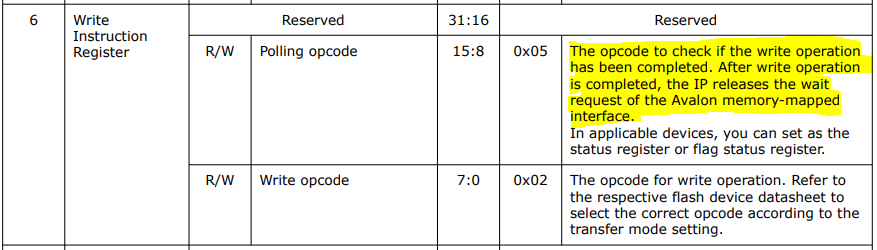

On the GSFI User Guide I see that I can set a "polling opcode" in the Write Instruction Register of GSFI in order to make the GSFI do the polling automatically. Unfortunately this doesn't work.

I set the register = 0x00007038 since 0x70 = Read Flag Status Register opcode and 0x38 = 4-byte write opcode.

I'm using flag status register instead of status register since it's recommended for Micron's flash devices.

Am I doing something wrong? How can I use the integrated polling mechanism?

GSFI User Guide: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-gen-sfi.pdf

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you try with 4 bytes programming? Since you are using 4 bytes addressing. Probably can try with 34H?

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

the write per se isn't the problem. The polling instruction 0x70 is.

With 0x34 and 0x38 I see no differences. I think that once the flash is set to 4-byte mode, you can use both with the same effect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you try with that?

Meanwhile regarding to this, what do you mean by doesnt work? What is the response you got after executing the command?

Unfortunately this doesn't work.

I set the register = 0x00007038 since 0x70 = Read Flag Status Register opcode and 0x38 = 4-byte write opcode.

Regards,

Bruce

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

as I said, I already tried and I see no difference.

I wrote a test code which writes 2 blocks of data.

After I write a block of data into the flash memory, the peripheral is supposed to poll the Flag Status Register and wait for the write completion. I wrote 0x00007038 in register 6 of the peripheral as specified in the GSFI user guide:

Debugging the code I see that the peripheral doesn't wait and jump straight to the next write instruction, failing it (since it's too soon to write other data). I can see that the next block is not programmed.

So I added a software polling cycle which wait for the BUSY bit into Flag Status Register to clear. This works, but it's not the right way to do it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Maybe I was not so clear...I CAN set the 0x6 register with 0x00007038, with no errors. I do it when I initialize the GSFI peripheral.

It's the write instruction which fail to wait for the BUSY flag of the flash memory to clear.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I think you may want to poll the command to keep on reading flag status register until the busy is over. Executing 1 time might not be sufficient.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

yes that's what I'm doing, as I said in my first message. That's software polling.

However the GSFI peripheral has the ability to perform hardware polling. The peripheral itself can automatically poll a specified flash register in order to automatically check if the write process is done.

That's what is not working in my design.

I'd like to know how to configure it in order to do hardware polling, since I followed the user guide and the example but It doesn't work in the intended way.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just want to clarify with you, you are able to write 0x00007002 to perform opcode operation to read flag status register and then poll and read 0x00007002 again to check the flag status register right? Please clarify if this is wrong.

Also, what do you mean by hardware polling?

Regards,

Bruce

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page