- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

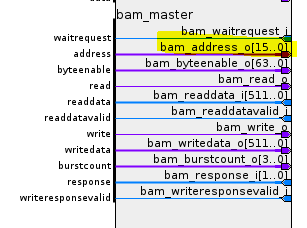

I am trying to interface HBM2 with pci express hard ip+ on stratix 10 MX. I am referencing to this example design https://fpgacloud.intel.com/devstore/platform/18.1.0/Pro/pci-express-gen3-x16-avmm-dma-with-hbm2-memory-reference-design/?wapkw=hbm2%20interface%20pci%20express , but in this I am not able to understand that how the BAM master address width is 30 bits whereas when I am generating the same IP inside my qsys system for the same configuration I am getting 16 bits as the address width. The BAR size in both of the cases is 16 bits.

Is there any way I can manually edit this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Sorry for the mistake.

I tried the same and I only can see the 16bits on the address. These address bits are affected by the setting of "Address width of bursting master" of the PCIe IP. I believe the developer hack the IP and change the address width to 30 instead.

If you need, you can change this by modifying the g3x16_hbm2_avmm_bridge_512_0.ip file.

Search for Address width of Bursting Master and you can change the value to 30.

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ok in this case we should able to spot the problem when we validate the design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @BoonT_Intel ,

I am a student from the same lab as @rsing108 , picking up this project where he left off. Has there been any update with this design validation?

We are specifically interested in the axi_bridge_to_hbmc_if.v design file, as we are still encountering issues in our own derived design that we think may be due to undiscovered bugs in this file.

Thanks!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »