- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

7 Replies

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @JHUAN157

In order for me to assist you.

Could you provide more info:

- what version of Quartus are you using

- what machine are you using? Windows/Linux?

- how to replicate

- what debug have you done so far

- have you tested on other machines

- does this happen to other IP or PLL IP only?

- does this happen to vhdl only? or verilog too?

- what are the other debug done?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

JW,

I am using Quartus II 64-bit Version 13.1.0, Microsoft Windows 10 Pro.

To replicate:

In the Quartus II Window, Tools -> MegaWizard Plug-In Manager

In the MegaWizard Plug-In Manager window [page 1], select “Create a new custom megafunction variation”, and click Next.

In the MegaWizard Plug-In Manager window [page 2], on the left column, click on PLL -> Altera PLL V13.1. On the right column, select VHDL, and put pll.vhd in the output file field. Click on Next

The Altera PLL window pops up. I did not change anything in the Altera PLL window. Everything is default. Click on Finish.

Error occurs. Error: Execution of script C:/Users/JASONH~1/AppData/Local/Temp/alt8116_4978854645064875100.dir/0002_pll_gen/proj.tcl failed

I have not tried other machines. I generated fifo.vhd from the FIFO IP with no errors. It happens to both vhdl and Verilog.

Thanks,

Jason

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

JW,

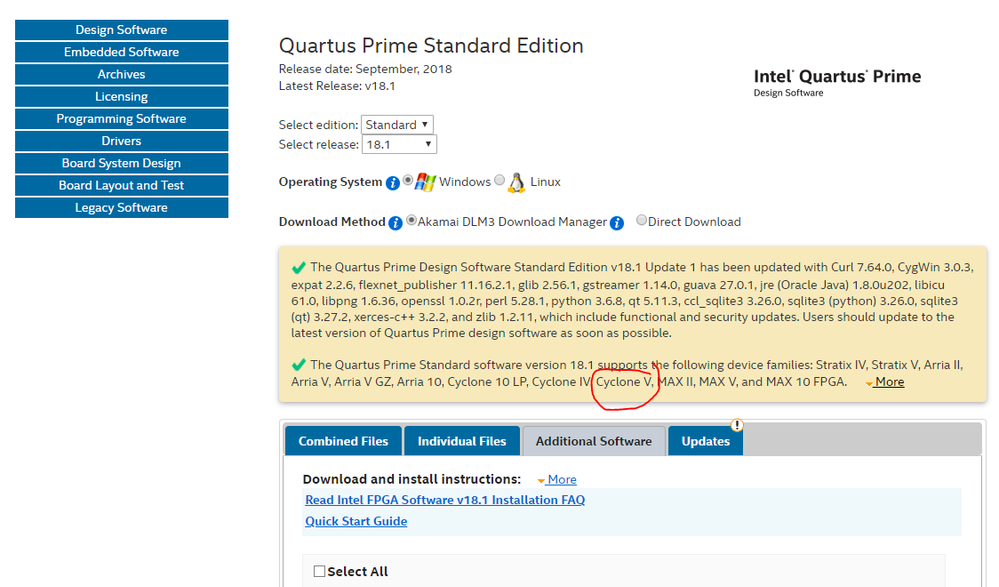

I am using Cyclone V GT FPGA Development Kit; not all the Quartus software support this device. For example, Quartus 18.1 does not support Cyclone V device.

Thanks,

Jason

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @JHUAN157

Are you referring to the Pro or Standard?

In the Standard Edition, 18.1 still supports Cyclone V.

http://fpgasoftware.intel.com/?edition=standard

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

CW,

I used Quartus Prime Standard Edition 18.1 to generate the PLL IP core successfully, but my design cannot be fit in the device. The error message says “Can’t fit design in device. Modify your design to reduce resources, or choose a larger device. …” My design can be fit in this device when I use Quartus II 13.1.

Thanks,

Jason

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @JHUAN157

When you couldnt instantiate PLL, i believe all logics that was driven by your PLL was synthesized away. That's why it can fit.

I believe now that you can successfully instantiate your PLL, your logics are NOT synthesized away anymore. That's why you CANNOT fit.

In that case, you will have to revise your design to lesser resources or select a larger device.

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page