- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear sir,

I encountered the following problems when using FFT IP core to simulate

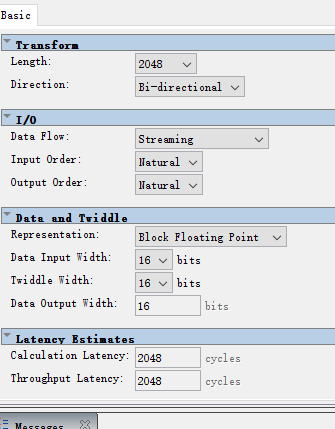

My FFT IP core configuration is as follows.I configure it as IFFT.

In the case of entering the same data,

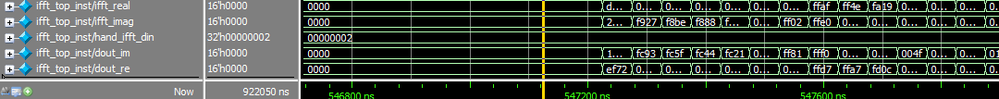

Sometimes, I can get the right results, as shown in the following figure:

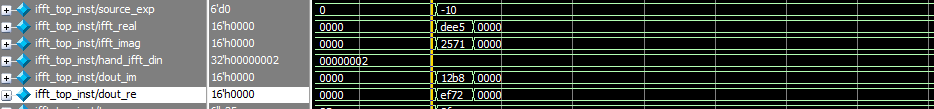

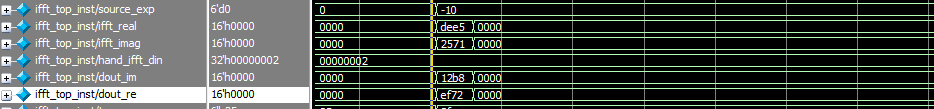

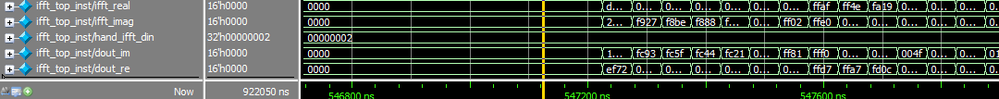

But sometimes, I always get wrong results, as shown in the following figure:

What may be the cause of this abnormal output?

We are looking forward to your reply.

- Tags:

- IFFT-modelsim

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello xiangxufu,

Thank you for posting on the Intel® communities.

We would like to inform you that we have a forum for FFT Intel® FPGA IP Core issues and questions, so we are moving it to the "FPGA Intellectual Property" forum so you can get better support for this matter.

https://community.intel.com/t5/FPGA-Intellectual-Property/bd-p/fpga-intellectual-property

Best regards,

Sebastian M

Intel Customer Support Technician

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sebastian:

Thank you very much for your reply!

Xiangxufu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. The case has just been routed to me. As I understand it, you observe some issue with the FFT IP in simulation. To ensure we are on the same page, just would like to check with you on the following:

1. What is the specific device and Quartus version that you are using?

2. Just would like to check with you if you have had a chance to try with "Variable Streaming" + "Fixed Point"?

3. Just would like to check with you if you have had a chance to try simulating with the IP generated example design to see if similar issue persists?

Please let me know if there is any concern. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for you reply.

My platform is bladeRF software radio, the chip is 5CEBA9F23C8, quartus version is 17.1, modelsim version is 10.6d.

In a project, I use the following script command to compile the ifft file:

1. vlog -vlog01compat -work nuand +incdir+G:/bladeRF/hdl/fpga/user/src/trans {G:/bladeRF/hdl/fpga/user/src/trans/ifft_top.v}

2. vlog -vlog01compat -work nuand +incdir+G:/bladeRF/hdl/fpga/user/ip/trans/ifft/ifft/synthesis {G:/bladeRF/hdl/fpga/user/ip/trans/ifft/ifft /synthesis/ifft.v}

3. vlog -sv -work nuand +incdir+G:/bladeRF/hdl/fpga/user/ip/trans/ifft/ifft/synthesis/submodules {G:/bladeRF/hdl/fpga/user/ip/trans/ifft /ifft/simulation/submodules/ifft_fft_ii_0.vo}

4. vcom -93 -work nuand {G:/bladeRF/hdl/fpga/user/ip/trans/ifft/ifft/synthesis/submodules/auk_dspip_math_pkg.vhd}

5. vcom -93 -work nuand {G:/bladeRF/hdl/fpga/user/ip/trans/ifft/ifft/synthesis/submodules/auk_dspip_lib_pkg.vhd}

The following simulation results appear

In another project, I used the following script command to compile the ifft file:

1. vlog -vlog01compat -work work +incdir+G:/trans_sim_tx/user/src/trans {G:/trans_sim_tx/user/src/trans/ifft_top.v}

vlib ifft

vmap ifft ifft

2. vlog -vlog01compat -work ifft +incdir+G:/trans_sim_tx/user/ip/trans/ifft/ifft/synthesis {G:/trans_sim_tx/user/ip/trans/ifft/ifft/synthesis/ifft.v}

3. vlog -sv -work ifft +incdir+G:/trans_sim_tx/user/ip/trans/ifft/ifft/synthesis/submodules {G:/trans_sim_tx/user/ip/trans/ifft/ifft/simulation/submodules/ifft_fft_ii_0 .vo}

4. vcom -93 -work ifft {G:/trans_sim_tx/user/ip/trans/ifft/ifft/synthesis/submodules/auk_dspip_math_pkg.vhd}

5. vcom -93 -work ifft {G:/trans_sim_tx/user/ip/trans/ifft/ifft/synthesis/submodules/auk_dspip_lib_pkg.vhd}

The following simulation results appear

Through matlab simulation, confirm that the output of the second project is correct

I think there is no difference between the two compilation processes. The data sent at the same time is the same, but the simulation results are different. What might cause such an abnormal situation.This is my problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. For your information, in the FFT IP, you can generate the example test bench from IP -> Generate -> Generate Example Design -> ... Design. It is recommended for you to generate and refer to the example test bench. You may pay attention on the msim_setup.tcl file is generally used to compile all the required files for the FFT IP simulation.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page