- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I have an A10SOC Kit Board.

IN intel design store, I found a Multiple - Rate 10GE design example on A10SOC Kit Brd as below link :

I can compile it , then want to test it on my A10SOC KIT Board, using 【Quaratus -> System Console】with JTAG. Unfortunately tcl script report errors :

"

% cd hwtesting/system_console

% source main.tcl

% TEST_PHYSERIAL_LOOPBACK 0 1G 10000

CONFIGURE CHANNEL 0

configure_to_1G

error: master_write_32: This transaction did not complete in 60 seconds. System Console is giving up.

while executing

"master_write_32 $port_id $address $wdata"

(procedure "reg_write" line 7)

invoked from within

"reg_write $PHY_IP_BASE_ADDR $seq_control 0x111"

(procedure "SETPHY_SPEED_1G" line 8)

invoked from within

"SETPHY_SPEED_1G"

(procedure "CONFIG_1PORT" line 12)

invoked from within

"CONFIG_1PORT $speed_test"

(procedure "TEST_PHYSERIAL_LOOPBACK" line 10)

invoked from within

"TEST_PHYSERIAL_LOOPBACK 0 1G 10000"

。。

"

==

from project *qsf file, the pin defination are :

set_location_assignment PIN_AG29 -to mm_clk

set_location_assignment PIN_U29 -to ref_clk_1g

set_location_assignment PIN_AL29 -to ref_clk_10g

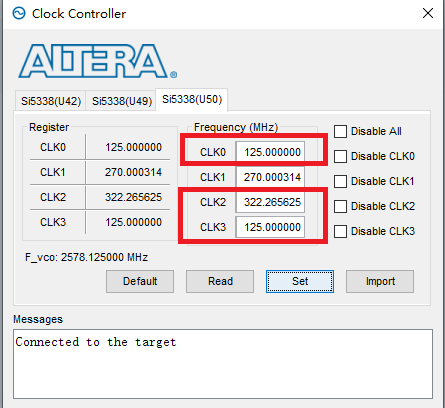

so I had launched "Clock Control " to re-programe Kit Board U50 ( Si5338B ) to :

-> CLK0A/B = 125MHz for "mm_clk"

-> CLK3A/B = 125MHz for "ref_clk_1g"

-> CLK2A/B = 322.265625 MHz for "ref_clk_10g"

have anyone run the same design test successfully on A10SOC Kit Board before ? any suggestion r appreciated ?

Thanks a lot !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

after following the design user guide ( https://www.intel.com/content/dam/altera-www/global/en_US/uploads/3/38/Arria_10_SOC_Scalable_Multispeed_10M-10G_Ethernet_Design_user_guide.pdf ),

to set " U50 CLK0A/B = 100MHz for "mm_clk" input ", the System Console can work as expect, I can run test using this example design on A10SOC KIT Board,

Thanks all for helps.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @DeshiL_Intel , for feedack about the missing "user guide document" problem.

Actually I tried the design example as above, and found some problem here, so we definitely need that userr guide to move forward. Would you please take a look of this issue as well. Thanks very much //

best reagrds

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jet,

Let's wait for Intel IT to fix the doc link so that we can checkout the user guide doc to find out is there any special guideline that we need to watch out in using this ref design.

The system console prompt timeout error which typically caused by either JTAG connection issue or Avalon MM bus stuck issue.

- For the time being, you can also try to reduce JTAG frequency to 16MHz or even 6MHz to see if it helps.

- Also pls ensure you are using the same Quartus version as the shown in ref design to avoid IP upgrade compatibility issue

- Pls check to ensure your Ethernet design is not stuck in reset

- Lastly, pls double check to ensure there is only one system console window open and you are not running other application like BTS or clock GUI or NIOS II terminal command sheel and etc to avoid JTAG congestion issue

Thanks

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

after following the design user guide ( https://www.intel.com/content/dam/altera-www/global/en_US/uploads/3/38/Arria_10_SOC_Scalable_Multispeed_10M-10G_Ethernet_Design_user_guide.pdf ),

to set " U50 CLK0A/B = 100MHz for "mm_clk" input ", the System Console can work as expect, I can run test using this example design on A10SOC KIT Board,

Thanks all for helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Alright, it's good to know you get it working now.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @DeshiL_Intel , may I ask an additional question ?

I see in ./hwtesting/system_console/main.tcl script, there's below command :

proc CONFIG_SFP_A_B_RATESEL {} {

puts " CONFIGURE SFP A "

reg_write 0x300000 0x4 0x1460

puts " CONFIGURE SFP B "

reg_write 0x300000 0x4 0x1660

}

what's the meaning of the Register_operation : reg_write 0x300000 0x4 0x1460 && reg_write 0x300000 0x4 0x1660 ?

Where can I find document to describe these Registers Functions in this design ? ? Do you know this ?

Thanks

/jet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jet,

User guide doc is meant to provide instruction steps to guide user on how to use the example design only while your question is more towards design implementation side.

Unfortunately there won't be any doc to describe on low level reg control for design implementation.

- It's expected for user to slowly trace the Quartus design connection and tcl script to find out what's what.

- Anyway, we don't share Max V CPLD software source code hence I don't think it's helpful for you to do the tracing either

To answer your question at high level,

- The SFP+ module should also has a PHY chip inside where user can access and configure these register.

- The SFP+ register function that you are looking at is for SFP data rate setting. SFP+ signaling rate selection, 0 <4.25 GBd, 1 > 4.25 GBd

- However, SFP+ reg access is not straight forward. I traced the design and board schematic and found out the Eth example design address 0x300000 is applied to FPGA SPI interface which is then connected to Max V CPLD on board. Finally MAX V CPLD uses I2C interface to communicate to SFP+ module.

Thanks.

Regards,

dlim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI @DeshiL_Intel , Thanks for your efforst to dig more for my query. I understand.

I will check details of this example design, hope I can find more information inside. Thanks a lot

best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jet,

You are welcome.

Alright, I am setting this case to closure.

Feel free to file new forum thread if you still have enquiry in future.

Thanks.

Regards,

dlim

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page