- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am creating pin planning for Arria 10ax057,

i used 2A Bank for GPIO with 1.8V my compilation was successful.

in other requirement i have to use LVDS pins, so i removed few GPIO's and taken few 13 sets of LVDS signals, and rest are 1.8V.

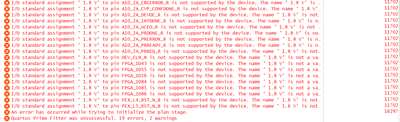

Now my fitter is giving error.

Error(11702): I/O standard assignment ' 1.8 V' to pin FPGA_IO43 is not supported by the device. The name ' 1.8 V' is not a valid I/O standard name

before using LVDS pins from the bank, i faced no issues

Queries:

1) In single bank can i use both LVDS and 1.8V ? If not suggest the document where i can find this information

2)Is it only 2A bank, (as PCIe hard ip reset is used from 2A) or it is same for all banks.

Regards,

Rajesh

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

How are you creating the assignment? Pin Planner? Assignment Editor? It looks like there's a space in front of 1.8 V that probably shouldn't be there.

You can also try running I/O Assignment Analysis from the Processing menu or Pin Planner. That might provide more detail on the issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You can refer to this document to see the requirement for LVDS: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/arria-10/a10_handbook.pdf

I would suggest to begin with page 101.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for reply.

as 2A bank is having configuration, and i used those as BIDIR . so it caused error.

when configuration pins ignored/taken as input to design the issue is solved.

Regards,

Rajesh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I’m glad that your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page