- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am trying to simulate an LVDS SERDES IP but don't seem to get DPA lock and with that never any data output. I am simulating with ModelSim Intel FPGA starter edition 2020.3.

IP Settings:

- Functional mode: RX DPA-FIFO

- Number of channels: 16

- Data rate: 1352.0 Mbps

- SERDES factor: 8

The data clock is running at 676 MHz and data is changing on both clock edges. The input data is toggling so there are plenty of edges provided on the input side. rx_fifo_reset is low for all channels and rx_dpa_reset starts out high but gets removed (goes low) when pll_lock goes high. Bit slip control is enabled but hardcoded to 0 for all channels.

The output clock rx_coreclock stabilizes and pll_locked goes high after about 600 ns but even after 4 us simulation time non of the channels rx_dpa_locked outputs go high.

Any help is greatly appreciated.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I figured out what the issue was:

I used the example design simulation as a comparison and eventually saw that the example locks only after over 8 us. This seems way longer than what the lock time specification in the device datasheet is specifying.

I then ran my own simulation for that long (before I had only run it up to 4 us as according to the lock time specification that is way more than should be needed) and it does also lock.

I am posting this in case someone else ever runs into this issue.

Thanks for the help along the way.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

May I know your OPN and which version of Quartus are you using?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using Quartus Pro 20.3.0.158 but Quartus is only used to generate the IP (originally created in Quartus 19 but upgraded with 20.3.0.158) the issue is in ModelSim Intel FPGA starter edition 2020.3.

I am not sure what OPN stands for.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

OPN is Ordering Part Number. Please provide me your OPN so I can help you further on your inquiry.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@AminT_Intel , do you have an estimate on when you could have an update on this?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Thank you for your patience and I hope you are doing well there. Would it be possible for you to provide me a design example?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Attached please find the design and testbench. When you unzip the file you will find a readme.txt that has instructions on how to run the simulation.

I am looking forward to your help resolving this issue of the DPA lock from the serdes never going high.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Can you send me in Quartus Prime Project File form? (.qpf, .qar, .par)

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The problem is in simulation not in hardware. I didn't even have a quartus project yet. However I created one just to be able to archive it as a qar file. Please see attached.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

These are the libraries I am using if this helps:

vlog -sv -work altera C:/intelFPGA_pro/20.3/quartus/eda/sim_lib/altera_mf.v

vlog -sv -work altera C:/intelFPGA_pro/20.3/quartus/eda/sim_lib/mentor/cyclone10gx_atoms_ncrypt.v

vlog -sv -work altera C:/intelFPGA_pro/20.3/quartus/eda/sim_lib/cyclone10gx_atoms.v

vlog -sv -work altera C:/intelFPGA_pro/20.3/quartus/eda/sim_lib/altera_lnsim.sv

And these are the modules I am compiling for simulation:

vlog -work work ../src/ip/dpaSerdes/altera_lvds_core20_191/synth/altera_lvds_core20_pll.v

vlog -sv -work work ../src/ip/dpaSerdes/altera_lvds_core20_191/synth/altera_lvds_core20.sv

vlog -sv -work work ../src/ip/dpaSerdes/altera_lvds_core20_191/synth/dpaSerdes_altera_lvds_core20_191_qxd6ljq.sv

vlog -work work ../src/ip/dpaSerdes/altera_lvds_1950/synth/dpaSerdes_altera_lvds_1950_gu4p3ni.v

vlog -work work ../src/ip/dpaSerdes/synth/dpaSerdes.v

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I will need to clarify your problem statement. Does the DPA lock not available from the beginning or after after 4 us? It seemed like from your problem statement that we should be expecting DPA lock if you are using DPA mode.

Can you please put your specification on your first comment to LVDS SERDES IP and run 'Generate Example Design' and let me know what you found.

Screenshots from your end about your issue will also be helpful for me to assist you.

In the meantime, you can also refer to our LVDS SERDES IP Guide from this link: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_altera_lvds.pdf

Thank you,

Amin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As stated in my first comment, DPA lock does NOT go high EVER, not at the beginning and still not after 4 us simulation time.

Have you run the simulation I provided at all? The reason I provided it was so you can re-create the issue on your end and help. You can see the issue described clearly in there.

I have already reviewed the LVDS SERDES IP Guide and am following the design recommendations.

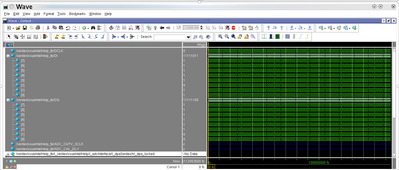

Attached is a screenshot of my simulation that shows that non of the serdes channels ever get DPA lock even though the data lines are all constantly toggling.

If you can PLEASE take a look at the simulation and help me understand why DPA lock never happens I would greatly appreciate it.

I have also attached the result of running generate example design hoping this helps.

Thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@AminT_Intel, do you have an estimate when you think you can have an update on this?

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I understand your frustration and I appreciate your patience. I have looked on your design and I found that there is no data on your DPA SERDES. I would advise you to follow the step on this video: https://www.youtube.com/watch?v=rvAByFs4G7c and let me know if you still run the same issue.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Amin! I have created the simulation from the example design. In that simulation DPA lock does happen but I can not figure out what the difference is to my simulation that does not get DPA lock.

You said you found there is no data on my DPA SERDES. I don't understand. The screenshot you attached shows that the data inputs are all toggling. Why do you say there is no data? I have changed the data input to match the example design simulations data input (input data high for 1 clock then low for 3 clocks and the data being offset by 90 degree phase from the inclock) but I am still not getting DPA lock in my simulation.

Is there any way you can still help to figure out what the issue in my simulation is and what I need to change to get DPA lock?

Thank you for your help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just realized you may mean that when you run the simulation you don't get waveform data for the signal rx_dpa_locked. I don't know why this would be when I run the simulation I do get data for that signal but it is always low. See attached screenshot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I figured out what the issue was:

I used the example design simulation as a comparison and eventually saw that the example locks only after over 8 us. This seems way longer than what the lock time specification in the device datasheet is specifying.

I then ran my own simulation for that long (before I had only run it up to 4 us as according to the lock time specification that is way more than should be needed) and it does also lock.

I am posting this in case someone else ever runs into this issue.

Thanks for the help along the way.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page