- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

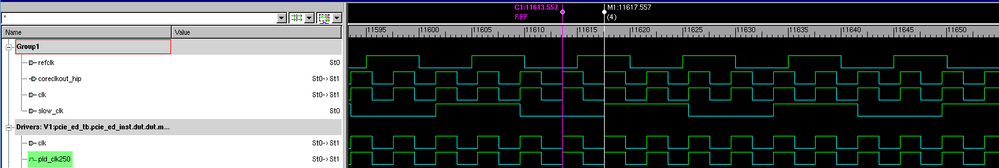

In the user guide, with H-tile types - Gen3x8, application clock or coreclkout_hip frequency = 250 MHz. But I could not verify it in the TA clock report.

Instead, I could see

"dut|dut|hip|altera_pcie_s10_hip_ast_pipen1b_inst|altera_pcie_s10_hip_ast_pllnphy_inst|g_phy_g3x8.phy_g3x8|phy_g3x8|xcvr_hip_native|ch0"

and its frequency is 500 MHz.

It matches the constraints below:

set clk_source_freq "250.0 MHz"

set datarate_100m 80

...

# 500M for aibx2 clocks if BW less or equal 64G

} elseif { [expr $datarate_100m * 8] <= 640 } {

dict set multiply_factor_dict aib_internal_div 2

dict set divide_factor_dict aib_internal_div 1

dict set multiply_factor_dict clkout 1

dict set divide_factor_dict clkout 1

}

...

create_generated_clock \

-name $inst|xcvr_hip_native|ch${channels} \

-source $no_inst_tx_internal_div_reg \

-master_clock $tx_internal_div_reg_name \

-multiply_by [dict get $multiply_factor_dict clkout] \

-divide_by [dict get $divide_factor_dict clkout] \

$no_inst_tx_clkout -addI think this clock is transport-layer clock and it is used to derive application clock/ coreclkout_hip / pld_clk250 as in the code below

assign coreclkout_hip = enable_512adapter_hwtcl? pld_clk250 : coreclkout_hip_wire ;

...

altera_ep_g3x16_avst512_io_pll_s10 altera_avst512_iopll (

.outclk_0 (pld_clk250),

.refclk (coreclkout_hip_wire),

.rst (~pin_perst),

.locked (iopll_locked),

.permit_cal (serdes_pll_locked_wire)

);

Do I understand it correctly?

If it is correct, then, it is confusing to me. Here is what I found.

I use application clock / coreclkout_hip as the refclk of PLL to derive another clock domain (200 MHz). The setting of PLL is

- Reference clock = 250 MHz

- Output clock = 200 MHz

However, when re-check the TA clock report:

- Reference clock = 500 MHz

- Output clock = 400 MHz

what is wrong here?

My platform is Stratix 10 MX | Quartus Prime Pro ver 22.2

Thank you,

TN

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I think that indicates the Clock Fmax.

If you changed the optimization Mode from Balanced to Aggressive Area you can achieve the 500MHz.

The Fmax specification is based on the fast clock used for serial data.

The interface Fmax is also dependent on the parallel clock domain which is design dependent and requires timing analysis.

Hope this clarified.

Regards,

Wincent_Intel

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Apologize for late reply, as I am looking at the design provided by you.

I am able to replicate your issue based on the MCDMA design provided in the IP catalog of H-tile.

I am getting the same result as yours which is 500MHz.

The next action I will do is to raise an internal ticket to the responsible team.

Temporarily we do not have any solution to this issue, expected to be fixed in next release version of Quartus.

I will update you if there is any update from the related team.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Thanks for the confirmation and your support.

I think you can close the case now.

Regards,

TN

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your understanding. I just close in my support portal.

This thread still remain for public command, I will keep you in post if there is any update related team.

If you have a new question, feel free to open a new thread to get support from Intel experts.

If you feel your support experience was less than a 9 or 10,

please allow me to correct it before closing or let me know the cause so that I may improve your future support experience.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The input clock frequency of H-Tile MCDMA(intel_pcie_mcdma) is 250 MHz and the IP runs on 250MHz only. Please refer the attached snippet.

The paths shown in the timing report are the QHIP paths and not inside MCDMA.

Time period = 4ns. Clock Frequency(dut.dut.mcdma.clk)= 250 MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent,

Sorry for my late reply due to holiday.

From your attached snippet, one thing can be confirmed is MCDMA clock is 250 MHz.

Your statement:

@wchiah wrote:The paths shown in the timing report are the QHIP paths and not inside MCDMA.

And because the reference clock of PLL is taken from "coreclkout_hip".

It means the reference clock is QHIP paths and it is not 250 MHz, isn't it?

Regards,

TN

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

My answer should be yes for your question.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your confirmation.

That clears my doubt.

That means '''coreclkout_hip' is not 250MHz as specified in the user guide.

Regards,

TN

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »