- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

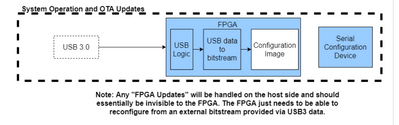

i want to know about OTA configuration process on Cyclone V FPGA

we are using Cyclone V E series FPGA and want to interface QSPI flash for FPGA configuration and also may be for some data.

QSPI flash will be having sort of two partition one will have default/backup FPGA configuration image and other partition will have reflashable configuration image, we want to have FPGA design such that it will receive OTA (over the air) FPGA bistream file over the USB interface which (image) need to be flashed in QSPI flash through fpga only not through any external device / processor and nor by Nios ip block. Then make FPGA to boot from new Flash configuration image through AS interface.

so for this setup please guide us for what IP core we need to use , which interface need to be used and where should be flash memory attached on IO. required a design Flow. what will be max working clock frequency can be.

FPGA = cyclone V E A4 series (non HPS version)

QSPI FLASH = MT25QU256 or MT25QL512

thanks & Regards!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

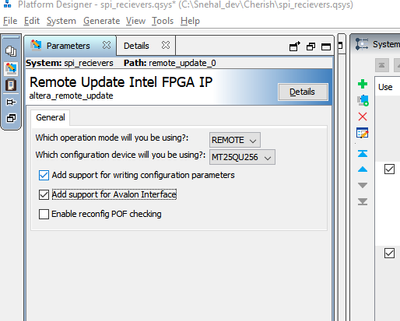

Hi, you may use remote update IP to do the OTA on cyclone V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi yaun,

thanks for the reply, i have some doubt for using remote update IP

1] for using this IP do we need to connected external flash memory to dedicated AS configuration IO on Cyclone V FPGA for QSPI flash

2] what is max frequency at which we can run this IP and configuration?

also I tried instantiating with below settings but getting error.

Error (169310): Design has remote update block "axi_control_block:axi_control_block_i|spi_recievers:spi_recievers_i|spi_recievers_remote_update_0:remote_update_0|altera_remote_update_core:remote_update_core|sd1", but the selected configuration scheme "Passive Serial" does not support remote update

Did we miss something , kindly help us to solve this

thanks & regards!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please find my response below:

1] for using this IP do we need to connected external flash memory to dedicated AS configuration IO on Cyclone V FPGA for QSPI flash

Yes, you need to connect QSPI flash with it.

2] what is max frequency at which we can run this IP and configuration?

20MHz for Cyclone V.

3) Error (169310): Design has remote update block "axi_control_block:axi_control_block_i|spi_recievers:spi_recievers_i|spi_recievers_remote_update_0:remote_update_0|altera_remote_update_core:remote_update_core|sd1", but the selected configuration scheme "Passive Serial" does not support remote update

It seems like you have selected "Passive Serial" in the setting? Can you change it to “Active Serial”?

“tools -> Device and Pin Options -> Configuration -> Configuration Scheme”

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page