- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

During the generation of my system I get this error:

Error: altgx_internal: error copying "C:/intelfpga/19.1/quartus/../ip/altera/ip_compiler_for_pci_express/lib/altpcie_serdes_4sgx_x4d_gen2_08p.v": no such file or directory

while executing

"file copy -force $source_file $outdir/$output_file"

(procedure "my_generation_callback" line 73)

invoked from within

"my_generation_callback"

I checked and the folder C:\intelFPGA\19.1\ip\altera\ip_compiler_for_pci_express is missing from the installation, do you know how to solve this problem?

Thank you,

Leonardo

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Leonardo,

Yes, I replicated the same problem in v19.1std and already reported this matter to the Intel PSG engineering team to fix it.

Besides, I have also tested in v18.1std, the same problem does not happen, and probably you can use v18.1std as the temporary workaround.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried to copy that folder from 18.1 and seem to work in 19.1, anyway thank you and keep us up to date when a fix come out

Regards,

Leonardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Another strange thing of the altera_pcie_hard_ip with stratix iv and v19.1std, it's impossible to use PCI-E Gen2 x8, in Platform Designer (ex QSys) I get the following message when setting parameters..

Error: system.pcie.pcie_internal_hip: Stratix IV GX and Arria II GZ Phy do not support Gen2 x8

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that could be one of the possible workarounds.

As per the user guide, table 1-2, Gen2 x8 is not supported.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_pci_express.pdf

When you configure it as Gen2x8 in v18.1, you will also notice the same error.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

These statements then are not clear if Gen2 x8 is not supported:

Stratix IV GX devices with speed grades C2/C2x/C3/I3 should be used to support PCIe Gen2 x1/x4/x8.

https://www.intel.co.uk/content/www/uk/en/products/programmable/fpga/stratix-iv.html

The Stratix® IV GX FPGA is fully compliant with PCI-SIG* for PCI Express* (PCIe*) Gen1 and Gen2 (x1, x4, and x8) and is on the PCI-SIG* integrators list

Regards,

Leonardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What you are using is Avalon-MM Interface, and it only supports up to Gen2x4 for the Stratix IV device. For Gen2X8 support, it uses the Avalon-ST interface, however, the PCIe Avalon-ST IP GUI is no longer available in v19.3. Table 1-5 in the link below show the difference between the Avalon ST and Avalon MM for Stratix IV device and others:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_pci_express.pdf

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the clarification.

I am reverting back on Q18.1 to use PCIE, just in case, to avoid any problem.

I was trying to compile some example of the DE4 dev board but internal timing of the PCI IP are failing:

pcie|pcie_internal_hip|stratix_iv.stratixiv_hssi_pcie_hip|coreclkout setup slack -1.194

Is something that can be ignored?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You probably need to check if the failing location is from the two different clock sources. If no, you can't simply ignore it.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

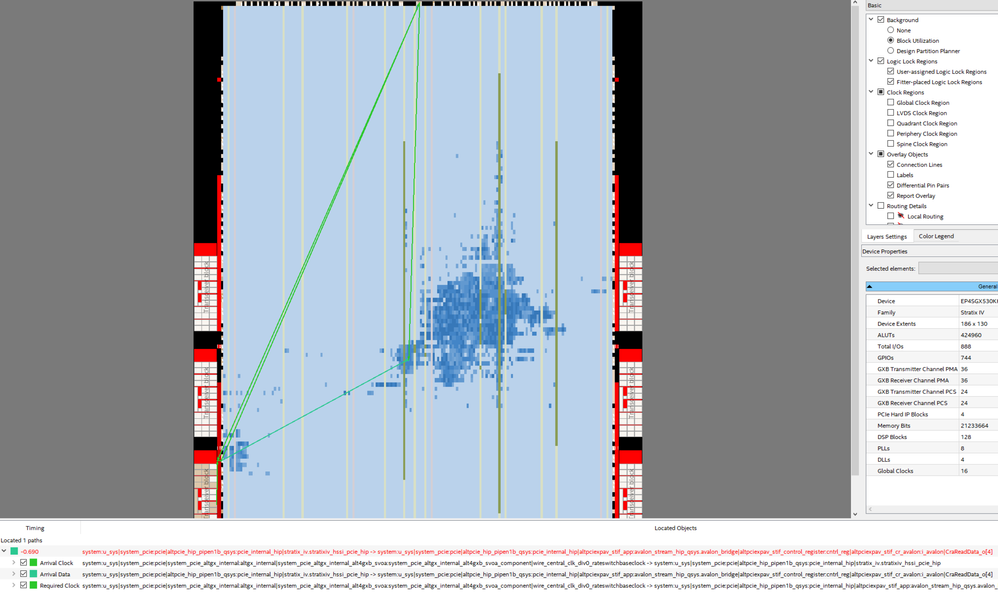

Hello, this is the main timing failure

Slack -0.690

From Node system:u_sys|system_pcie:pcie|altpcie_hip_pipen1b_qsys:pcie_internal_hip|dl_ltssm[4]

To Node system:u_sys|system_pcie:pcie|altpcie_hip_pipen1b_qsys:pcie_internal_hip|altpciexpav_stif_app:avalon_stream_hip_qsys.avalon_bridge|altpciexpav_stif_control_register:cntrl_reg|altpciexpav_stif_cr_avalon:i_avalon|CraReadData_o[4]

Launch clock u_sys|pcie|pcie_internal_hip|stratix_iv.stratixiv_hssi_pcie_hip|coreclkout

Latch clock u_sys|pcie|pcie_internal_hip|stratix_iv.stratixiv_hssi_pcie_hip|coreclkout

Relationship 4.000

Clock skew -0.311

Data delay 4.296

I was thinking that the timing of the hard ip were fixed and guarantee, this is the chip planner picture

Thanks

Leonardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I don't see this timing violation when I compile the Strativ IV PCIe IP in v18.1. If more help is needed, you may attach a simple design that can replicate this violation here, so that I can look into it.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I will set this case to close-pending for now. Please do not hesitate to get back to me within the next 20-day close-pending period if more help is needed.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

I still see the same problems as in the orginal post (i.e. missing files when trying to generate the code from QSYS) in version 20.1.1.720 Standard edition.

I wonder, is there is a plan to fix this. When reading the INTEL WEB pages Stratix IV devices seem to be fully supported in this version.

Another question I have is: what is the preferred IP core to be used for PCIe Express designs using the Stratix IV family ? (And what Quartus version do I have to use ?)

Best regards

Hermann

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page