- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

My environment: 10AS016E4F29, with Quartus pro 22.4.

Today I met a problem.

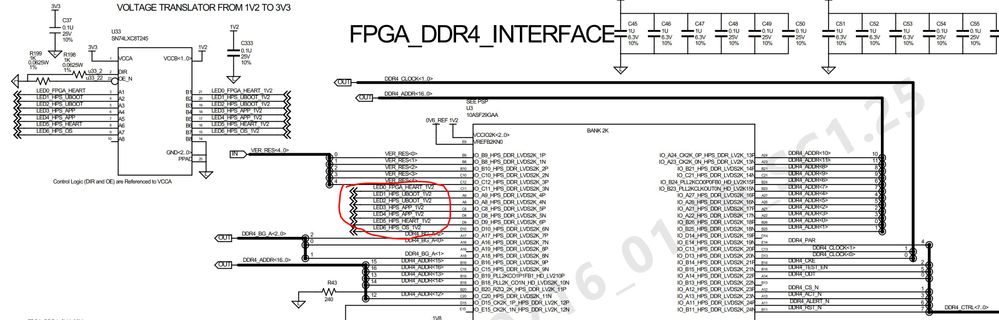

In my design, we used the DDR4 chip, the EMIF IP locates on bank 2J and 2K. and then I assigned some unused pins on bank 2K for general purpose.

For example, below 7 pins are used for LED flashing to indicate some status of internal logic.

LED0_FPGA_HEART_1V2

LED1_HPS_UBOOT_1V2

LED2_HPS_UBOOT_1V2

LED3_HPS_APP_1V2

LED4_HPS_APP_1V2

LED5_HPS_HEART_1V2

LED6_HPS_OS_1V2

On top file, I write a module to generate a low frequency pulse which is used to flash the LEDs. And the I assigned this pulse to the LEDs, as below shows.

Per my test, the LEDs I listed above which locate on 2K bank can’t flash, but other LEDs on other bank can be flashed with the same signal driving.

Below is the pin assignment for your information.

Then I did some test for this issue.

If I instantiate the EMIF, these LEDs will always light even I send the low frequency pulse to drive them.

But if I delete the EMIF, these LEDs then can be driven to flashing by the same pulse.

in face i have discussed this topic with Richard by mails because he gave me strong support on other topics, but I would like to open a new case here for this topic to let you know the workload of your supporting team.

I don’t know if there is any coupling between the EMIF pins and the LED pins, although they locate in the same bank.

I remember the unused pins in the EMIF bank can be used as GPIO.

How can I control the LED normally with the EMIF instantiated in my system?

Very thanks for your support!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, FvM,

thank you for the reply.

yes, when I disable the EMIF, the pins can be driven normally. when I enable the EMIF, the pins can not be driven by logic.

and i also found an Article with ID 000079165 from intel website, it mentioned that if HPS EMIF is enabled, Lane 3 of bank 2K can only be used as FPGA input only. I think this is the root cause.

But the article also mentioned that the Quartus Prime software version 15.1.1 and earlier do not check for these restrictions, and the patch for above restriction is also scheduled to be added to a future version of the Quartus Prime software. I used Quartus pro 22.4, the newest, it seems this version still not check this rectriction.

thanks again!

Rain.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"If you do not include any HPS external memory interface in your system, you can use banks 2K, 2J, and 2I in the Intel Arria 10 SX device as FPGA GPIOs.

If you include an HPS external memory interface in your system, adhere to these guidelines if you want to use the unused pins in banks 2K, 2J, and 2I for FPGA GPIOs:

• Bank 2K is used for SDRAM ECC, and address and command signals:

— Lane 3 is used for SDRAM ECC signals. You can use the remaining pins in this lane for FPGA inputs only.

— Lanes 2, 1, and 0 are used for SDRAM address and command signals. You can use the remaining pins in these lanes for FPGA inputs and outputs."

Did you disable HPS EMIF?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi, FvM,

thank you for the reply.

yes, when I disable the EMIF, the pins can be driven normally. when I enable the EMIF, the pins can not be driven by logic.

and i also found an Article with ID 000079165 from intel website, it mentioned that if HPS EMIF is enabled, Lane 3 of bank 2K can only be used as FPGA input only. I think this is the root cause.

But the article also mentioned that the Quartus Prime software version 15.1.1 and earlier do not check for these restrictions, and the patch for above restriction is also scheduled to be added to a future version of the Quartus Prime software. I used Quartus pro 22.4, the newest, it seems this version still not check this rectriction.

thanks again!

Rain.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rain,

When using HPS EMIF, the unused pin in Bank 2K lane 3 can only be used for FPGA inputs only.

Reference document: https://www.intel.com/content/www/us/en/docs/programmable/683106/21-1-19-2-0/restrictions-on-i-o-bank-usage-for-emif-19588.html

But you are not seeing any error message for checking this restriction when compiling the project design?

If so, can you share a design that can replicate this issue?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes, in fact, i am discussing this with Richard TAN on another section. and i have sent my project to him already.

you can check below link which demonstrate an internal error that Quartus pro 22.4 reported which triggered by this pin assignment restriction.

Quartus Prime pro reported error during full Compilation - Intel Communities

at first i have thought that these 2 topics are different issues so I opened different cases in different sections, but now I know both are caused by the pin assignment restriction.

but i think you still need to check why this pin assignment just trigger an internal error instead of the fitter error on quartus pro 22.4?

Richard had showed my when he compiled my design on your internal version quartus 23.1, the app reported the error with ID 18525.

thank you for the support!

Rain

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Rain,

Thank you for your feedback.

I will reach out to Richard for the design.

Since you have got the answer in this case, I will transfer this case to community support.

If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread.

Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page