- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We want to use a fractional pll with reconfiguration enabled in order to generate a core clock, synchronized to external timestamps. We use quartus 18.0.0 to generate an fPLL. Our problem is that we are noticing that the pll_cal_busy stays high and pll_locked stays low indefinitely. It looks like the clock on the output is not running.

We tried cycling pll_powerdown. This seemingly has no impact.

We tried triggering regeneration using the sequence in: https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/component/2017/why-does-the-fpll-not-lock-with-enable-phase-alignment-option-tu.html

It looks like the FPLL still stays in calibration mode indefinitely.

We found this post on the forum:

https://forums.intel.com/s/question/0D50P00003yyTeySAE/arria-10-fpll-lock-problem?language=en_US

Which looked like a similar issue. Adding to the project file:

set_global_assignment -name VERILOG_MACRO "ALTERA_XCVR_A10_DISABLE_RESET_CONNECTED_TO_CAL_BUSY=1"

This did make the clock to start running, the pll_cal_busy stays high and the pll_locked signal stays low. The strange thing is that reading the 0x280 register results in a 0x7, indicating that the PLL is locked.

We use an external clock generator IC as source for the FPLL in an Arria10 SoC FPGA. The output of this IC is configured by the hardware processor after booting. This means that the clock is not available during initial configuration of the FPGA fabric. Could this be an issue? We were assuming that this would be fixed by a pll_powerdown cycle and a recalibration.

We use a ALTCLKCTRL to be able to connect the FPLL ref clock to a normal clock input. Specifically IO_B2A_L13_CLK0_AB16_P of the 10AS027E4F29E3SG.

We would like some pointers on how to continue with the FPLL IP.

What is the impact of ignoring calibration?

Is my FPLL actually in lock or not?

How can we make the calibration actually finish?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May i know is that custom board or the Intel FPGA development kit ?

if it is dev kit , can you let me know which one ..so that I can create one example design and send to you ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sree,

That would be the Mercury+ AA1 module in combination with the Mercury+ PE1-400 from the company Enclustra.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ok...i am not sure about the board .but lets try to solve your issues ....Can you tell me which mode you are using the FPLL?

I would like to ask all the details of the FPLL setting in the IP and if could share that ..let me try with one of the board here ..

Thank you ,

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sree,

Thank you for the response and help in solving this issue.

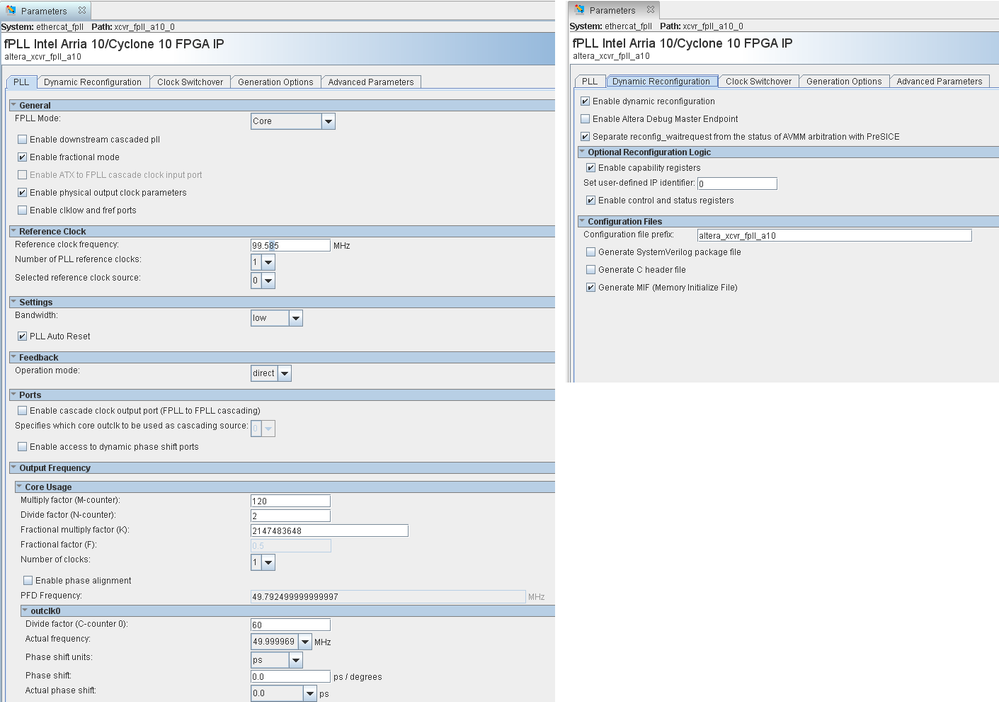

We use the FPLL in core mode as we want to use it as a core clock source. I included a screenshot of the settings I used, and attached a zip file of the fPLL IP.

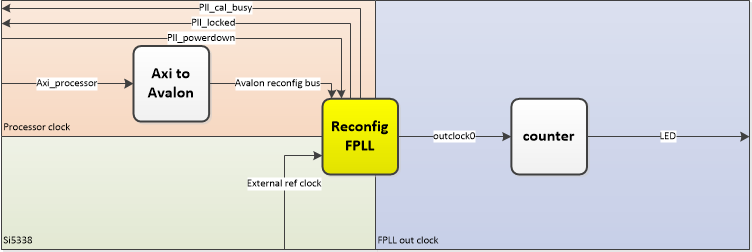

We convert the AXI bus from the Arria 10 hardware processor to Avalon and map it's range to the memory. The 'pll_powerdown', 'pll_locked' and 'pll_cal_busy' signals are connected to registers in the memory range of AXI bus.

The 'pll_refclk0' is generated from a SI5338 clock generator IC, which is also configured by the processor at boot up. It is set up to generate a 99.585 MHz clock.

Currently, the output 'outclk0' of FPLL is connected to a counter, that toggles an LED every 5000000 clock cycles.

Are you aware that this case was moved/copied to premiersupport.intel.com and was picked up by Pawel Makyla on the 22th of July?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

oh i am not aware of it ... Do you know the case number ? I can see the update in future :) ..

Thank you

Regards,

Sree

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, that would be: 00450911

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the case number ;

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page