- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Support,

I downloaded AN708_q170. try to run it in my quartus 21.3. after I update the IP.

the platform designer, told me

Error: top.DUT.dma_rd_master: DUT.rd_dts_slave (0x80000000..0x80001fff) overlaps emif_0.ctrl_amm_0 (0x0..0xffffffff)

Error: top.mm_clock_crossing_bridge_0.m0: emif_0.ctrl_amm_0 (0x0..0xffffffff) is outside the master's address range (0x0..0xfffffff)

Error: qsys-generate failed with exit code 3: 2 Errors, 5 Warnings

Error: top.DUT.dma_rd_master: DUT.rd_dts_slave (0x80000000..0x80001fff) overlaps emif_0.ctrl_amm_0 (0x0..0xffffffff)

Error: top.mm_clock_crossing_bridge_0.m0: emif_0.ctrl_amm_0 (0x0..0xffffffff) is outside the master's address range (0x0..0xfffffff)

Error: qsys-generate failed with exit code 3: 2 Errors, 5 Warnings

is there an PCIe with external memory example in 21.3 format. don't tell me that I have to install a quartus version 17.

Thanks,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I did some investigation and determined that Quartus 17.0 onwards don't allow test bench generation with critical hard blocks not connected. The reference design attached in AN708 was generated using Quartus 17.0 only. This Quartus version allows test bench generation with hip_pipe and hip_control conduit exported. My suggestion at the moment will be please revert back to Quartus 17.0 to use QYS feature to generate the test bench system.

To encounter this, I have opened an internal case to resolve this; so the AN708 simulation and test bench generation are also validated to allow migration. Hope the related team will work on this.

Please accept my apologies for the frustration you have faced. Hope this is clarified.

Regards,

Wincent_Intel

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel friends,

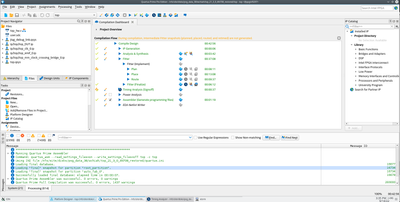

after some struggle, I can compile the projects. I have the following errors while I generate simulation example. could anyone give me some suggestion to solve the problem.

Error: Unexpected error writing the ensemble: java.io.FileNotFoundException: C:\intelfpga_pro\21.3\ip\altera\altera_pcie\altera_pcie_hip_256_avmm\channelizer\example_design\top.qsys (Access is denied)

Error: Unexpected error writing the ensemble: java.io.FileNotFoundException: C:\intelfpga_pro\21.3\ip\altera\altera_pcie\altera_pcie_hip_256_avmm\channelizer\example_design\sriov_mcdma_app_g3x8_256b.qsys (Access is denied)

Error: Unexpected error writing the ensemble: java.io.FileNotFoundException: C:\intelfpga_pro\21.3\ip\altera\altera_pcie\altera_pcie_hip_256_avmm\channelizer\example_design\rddc_mc_256b.qsys (Access is denied)

Error: Unexpected error writing the ensemble: java.io.FileNotFoundException: C:\intelfpga_pro\21.3\ip\altera\altera_pcie\altera_pcie_hip_256_avmm\channelizer\example_design\wrdc_mc_256b.qsys (Access is denied)

Error: can't read "intf_use_partner(pcie_rstn)": no such element in array

Error: Error: Unexpected error writing the ensemble: java.io.FileNotFoundException: C:\intelfpga_pro\21.3\ip\altera\altera_pcie\altera_pcie_hip_256_avmm\channelizer\example_design\top.qsys (Access is denied)

Error: There were errors creating the testbench system.

I attached the Quartus 21.3 compiled project, it can be compiled but not know anything else.

Thank you,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share with me how your resolved the compilation issue?

For error "Error: Unexpected error writing the ensemble: java.io.FileNotFoundException:"

Can you please check if The software was installed under Program Files folder ?

If YES, I would suggest you to try unistalled Quartus Suite and installed again on root directory (C:\Altera).

Probably the problem was the space in the installation path ("Program Files").

Hope this help,

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wincent_Intel

the Quartus was installed at C:\intelFPGA_pro\21.3

for the compilation,

1. did an IP auto update.

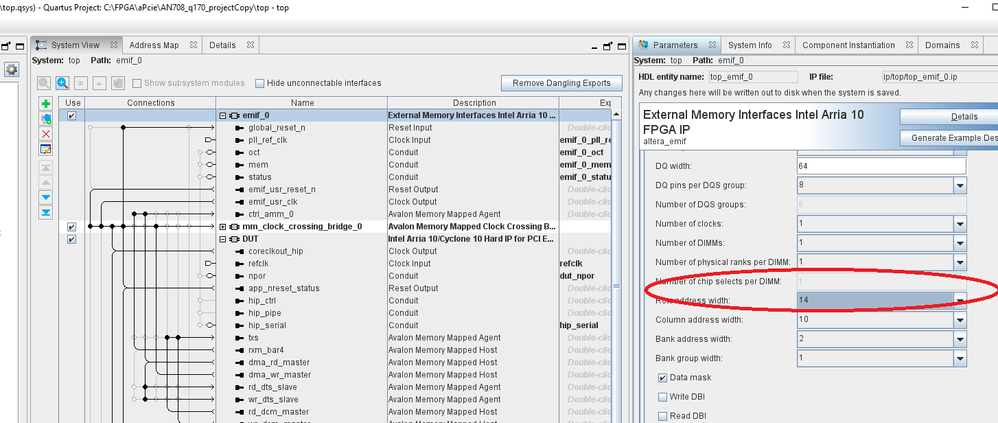

2. the new IP not support 12 bit CAS( or RAS I can't remember), first time I change it to 16 bits, then the error happens. after I change it to 14 bits. then it compile OK.

Thank you,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Can I know where you change the CAS/RAS bits ? is it inside platform designer ?

Hoping to hear back from you.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, use platform designer. original package set to 12bit. the first time I choose 16 bits. there is a conflict of the base address. after I change it to 14 bits, it compiled.

thank you,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dsun,

Can you share with me which/where is 12bits value you are adjusting ? Maybe a printscreen ?

I am interested to know the originally issue that might be causing the error so that I can further escalate this issue.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for reaching out.

Just to let you know that Intel has received your support request and I am assigned to work on it.

Allow me some time to look into your issue. I shall come back to you with findings.

Thank you for your patience.

Best regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for sharing with me.

for the Error: Unexpected error writing the ensemble: java.io.FileNotFoundException: issue

Normally You will receive the above mentioned error in the SOPC Builder if you have logged into a PC without admin priveleges

and you try and generate one of the example designs that is located in the default installation.

You can workaround this error by copying the example design from the installation directory into a new directory elsewhere on the PC.

Can you please try it ?

Regards

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I copied the project into a different directory, the software generates same error message.

by the way, I can run other very complex simulation with Jesd204b and DDR4 with Nios2 core without any problem.

I am learning PCIe now, don't know why I have this problem.

Thank you for helping.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

good news, after I change the owner of the directory, the original error disappeared.

bad news was that new errors appeared.

Error: can't read "intf_use_partner(pcie_rstn)": no such element in array

Error: Error: can't read "intf_use_partner(pcie_rstn)": no such element in array

Error: There were errors creating the testbench system.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

by the way, could you duplicate the problem on your platform, if not, that means related to the tool installation. otherwise, is the project/software itself problem

thanks,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I set the testbench output directory to

C:/FPGA/aPcie/AN708_q170_projectCopy/top_tb/

why the tools want to update the files in the

C:\intelFPGA_pro\21.3\ip\altera\altera_pcie\altera_pcie_hip_256_avmm\channelizer\example_design?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Dsun,

Glad that the issue solve, are you using company workstation/computer ?

Suspect some file access routes might be encrypted...

For the new issue can you please remove all the unnecessary custom IP paths mentioned in IP Search Path and try to generate testbench again ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wchiah,

How to find the IP search path? how do I know which is unnecessary?

by the way, can Intel provide a version of AN708 that can run with Quartus 21.3. I am learning generic PCIe IP by Intel example. I am not an Intel Platform expert. can I assume that there are not many people use Intel PCIe ip on latest quartus software.

if it is not straight forward to me, hard to believe it is an easy job for other engineers.

I really appreciate your help to solve this problem, should it be Intel's responsibility to provide a working example on the latest platform?

is the latest release based on Quartus 17?

Thank you,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I understand your feeling. That is why I am here to help you.

I try the .qar file provided by you without modifying anything (just simple run full compilation)

Using Quartus Pro Edition 21.3 . The design is able to compile without any error at all.

Can you please try it again ? or on another laptop perhaps?

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wchiah

We are on the same page now. the project I uploaded can be compiled in Quartus 21.3.

My question/problem was

after open the top.sys at the platform designer.

when generate testbench system.

Error: can't read "intf_use_partner(pcie_rstn)": no such element in array

Error: Error: can't read "intf_use_partner(pcie_rstn)": no such element in array

Error: There were errors creating the testbench system.

as a new user to PCIe and DDR system, I think the simulation environment will be very helpful to make deep understand of the interface.

if the platform designer doesn't support to create the simulation environment automatically.

is it possible to create a simulation for this PCIe and DDR example?

How?

Thank you very much

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

I did some investigation and determined that Quartus 17.0 onwards don't allow test bench generation with critical hard blocks not connected. The reference design attached in AN708 was generated using Quartus 17.0 only. This Quartus version allows test bench generation with hip_pipe and hip_control conduit exported. My suggestion at the moment will be please revert back to Quartus 17.0 to use QYS feature to generate the test bench system.

To encounter this, I have opened an internal case to resolve this; so the AN708 simulation and test bench generation are also validated to allow migration. Hope the related team will work on this.

Please accept my apologies for the frustration you have faced. Hope this is clarified.

Regards,

Wincent_Intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wchiah,

Thank you very much for the investigation and a clear conclusion. it is very hard to get an ideal solution, but it is very critical to know what is going to happen, especially for a learner. I am not sure I would like to go to Quartus 17. I will spend more time to read ug_a10_pcie_avmm_dma-683425-666332. by the way, beside rely on AN708, is there other example with PCIe and DMA and DDR? the goal is to use PCIe in my application not AN708 itself.

appreciate you time and patience.

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David,

Is okay, I am happy if can help you. I believe you can be an expert somewhere in the future.

Meanwhile, we can learn together at the moment, I also learn quite a lot from the question you ask right now.

Thanks for actively reply and provide the needed information as well for us to further debug this.

For example related to Arria 10 either PCIe or DMA, you may refer to Intel FPGA design store.

Hope this answer your question,

Regards,

Wincent_Intel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page