- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

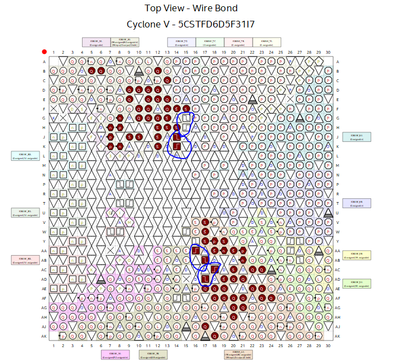

I'm designing an FPGA, using Enclustra Mercury PE1 and SA2. The FPGA is Cyclone V ST D6.

I'm trying to assign the data entry and clock pins. Someone knows if it is possible to connect the inclock input to any differential I/O. Or do I have to use dedicated clock pins (clk[0..7])?

Attach the image marking the pins dedicated to clk:

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I apologize for the late response. They can be connected to any differential I/O. The selection criteria is based on whether the clock is going to capture the data directly or going to drive the PLL. You can also use dedicated pins to drive the global network if they are high speed and big fanout. I hope this answer helps and again I apologize for the late response.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page