- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm trying to compile pcie_ed from agilex_agib027r29a1e2vr0_fpga_reva_v21.2b072_v1.0/examples/pcie_ed

using Quartus Pro 21.

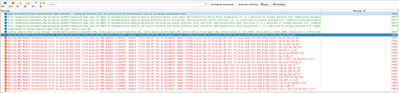

Opening the project, running the compilation:

Could you provide working example with at least no error when compiling...

1. Download here

it says "21.2 or higher"

2. I untar pcie_ed, pcie_ed.qpf has QUARTUS_VERSION = "21.1"

3. Open the qpf with Quartus 21.1, compile, errors

Please update the link ASAP with working examples.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the same tar, I tried to compile "qsfpdd_xcvr" on 21.1 (on 22.1 the Avalon Data Test Generator IP core doesn't exist...)

I don't find this error message very useful, any help would be very much appreciated.

Opening the "Support-Logic Generation" 's report, Quartus ends up crashing:

Problem Details

Error:

*** Fatal Error: Segment Violation: faulting address=0x10, PC=0x7f1a2607a6bd : 0x7f1a2607a6bd: db_tileip!TILEIP_WRITER::initialize_default_profile() + 0xc1

Module: quartus

Stack Trace:

Err Handler 0x111ab: ERR_UNWINDER_BACKTRACE::get_stack_trace(void const**, int, int, void*) + 0xf3 (ccl_err)

Err Handler 0x7429a: msg_ie_get_call_stack(void*) + 0xa3 (ccl_msg)

Err Handler 0x7588e: MSG_INTERNAL_ERROR::report_fatal(char const*, void*) + 0x3c (ccl_msg)

Err Handler 0x12b2d: err_report_fatal_exception(char const*, void*) + 0x68 (ccl_err)

Err Handler 0x135e6: err_sigaction_handler + 0x12f (ccl_err)

System 0x12ce0: (pthread)

Quartus 0x3d16bd: TILEIP_WRITER::initialize_default_profile() + 0xc1 (db_tileip)

Quartus 0x4093d8: TILEIP_WRITER::solve_tile(std::vector<std::pair<std::string, std::string>, std::allocator<std::pair<std::string, std::string> > >*, TILEIP_TILE*, std::string const&, bool, bool) + 0x4a (db_tileip)

Quartus 0x40973f: TILEIP_SOLVER_IF_IMPL::validate_placement(std::vector<TILEIP_SOLVER_IF::TILEIP_BB_PLACEMENT, std::allocator<TILEIP_SOLVER_IF::TILEIP_BB_PLACEMENT> >*, std::string const&, bool) + 0x133 (db_tileip)

Quartus 0x40094: TPL_FACADE::load_ip_json(std::string, nlohmann::basic_json<std::map, std::vector, std::string, bool, long, unsigned long, double, std::allocator, nlohmann::adl_serializer, std::vector<unsigned char, std::allocator<unsigned char> > >) + 0x104 (sys_tpl)

Quartus 0x7b78c: BPPS_MANAGER::load_design() + 0x440 (sys_bpps)

Quartus 0x7d90e: BPPS_MANAGER::initialize() + 0x32 (sys_bpps)

Quartus 0x60688: bpps_initialize_blueprint + 0x2e7 (sys_bpps)

Quartus 0x4c942: TclNRRunCallbacks + 0x42 (tcl8.6)

Quartus 0x4de7b: TclEvalEx + 0x68b (tcl8.6)

Quartus 0x4e496: Tcl_EvalEx + 0x16 (tcl8.6)

Quartus 0x1e3d9: atcl_tcl_eval(Tcl_Interp*, std::string const&, bool) + 0xe3 (ccl_atcl)

Quartus 0x6d718: ITC2_BPPS_CHANNEL_IMPL::doWork() + 0x598 (resr_itc2)

Quartus 0x6bdd1: ITC2_BPPS_CHANNEL_IMPL::qt_static_metacall(QObject*, QMetaObject::Call, int, void**) + 0xf1 (resr_itc2)

Quartus 0x2db023: QObject::event(QEvent*) + 0xd3 (Qt5Core)

Quartus 0x15b7ac: QApplicationPrivate::notify_helper(QObject*, QEvent*) + 0x9c (Qt5Widgets)

Quartus 0x162290: QApplication::notify(QObject*, QEvent*) + 0x1e0 (Qt5Widgets)

Quartus 0x2aba18: QCoreApplication::notifyInternal2(QObject*, QEvent*) + 0x108 (Qt5Core)

Quartus 0x2aea92: QCoreApplicationPrivate::sendPostedEvents(QObject*, int, QThreadData*) + 0x222 (Qt5Core)

Quartus 0x304851: QEventDispatcherUNIX::processEvents(QFlags<QEventLoop::ProcessEventsFlag>) + 0x41 (Qt5Core)

Quartus 0x2aa42a: QEventLoop::exec(QFlags<QEventLoop::ProcessEventsFlag>) + 0x10a (Qt5Core)

Quartus 0xb52b4: QThread::exec() + 0x84 (Qt5Core)

Quartus 0x1b41cc: AFCQ_THREAD::thread_wrapper(void*) + 0xe (gcl_afcq)

Quartus 0x40ed6: msg_thread_wrapper(void* (*)(void*), void*) + 0x64 (ccl_msg)

Quartus 0x1528e: mem_thread_wrapper(void* (*)(void*), void*) + 0x5e (ccl_mem)

Quartus 0xcdc0: err_thread_wrapper(void* (*)(void*), void*) + 0x1e (ccl_err)

Quartus 0x6ba5: thr_thread_wrapper + 0x15 (ccl_thr)

Quartus 0x1b3855: AFCQ_THREAD::run() + 0x13 (gcl_afcq)

Quartus 0xb65a5: QThreadPrivate::start(void*) + 0x135 (Qt5Core)

System 0x81ca: start_thread + 0xea (pthread)

System 0x39d83: clone + 0x43 (c)

End-trace

Quartus Prime Version 21.1.0 Build 169 03/24/2021 SC Pro Edition

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Welcome to INTEL forum. Can you give me a little background/elaborate on your setup proses and step? provide error messages?

For privacy, reply/attach your file in private message.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No need for privacy, I'm just trying to work with Intel's public projects.

1. https://www.intel.com/content/www/us/en/products/details/fpga/development-kits/agilex/i-series.html

2. Download the tar ES (21.2 or higher)

3.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

3. untar

4. open with quartus pro 21.1 or 22.1

5. agilex_agib027r29a1e2vr0_fpga_reva_v21.2b072_v1.0/examples/pcie_ed or any other example designs

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

6. try to compile the project

the website is really broken, it doesn't stop to move the view down, it's pretty annoying and impossible to write a simple message...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Could you provide the error message screenshot and the .log file

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Upon checking, the case is still in pending investigation by engineering. The fix will take some time. As suggested in community forum https://community.intel.com/t5/Intel-Quartus-Prime-Software/Avalon-Data-Pattern-Checker-IP-missing-in-Quartus-Pro-22-1/m-p/1390003#M73987

that is the best you could use back the older Quartus version which has the IP for now as a workaround.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have not heard from you and I hope that my last note clears up this matter. I will now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page