- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am working on the Altera Cyclone V Development board (revision D).

It seems that the FPGA image is not loaded after power up. I found following lines in the uboot bootlog: reading soc_system.rbf 7007184 bytes read in 2368 ms (2.8 MiB/s) altera_load: Failed with error code -4 My board switch and jumper settings are listed as below: SW1 All OFF SW2 All OFF SW3 1:ON 2:ON 3:ON 4:ON 5:ON 6:ON SW4 1:OFF 2:OFF 3:ON 4:ON J5 open J6 shorted J7 shorted J9 open J13 shorted J16 open J26 right shorted J27 right shorted J28 right shorted J29 right shorted J30 left shorted J31 shorted Please help- Tags:

- soc

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

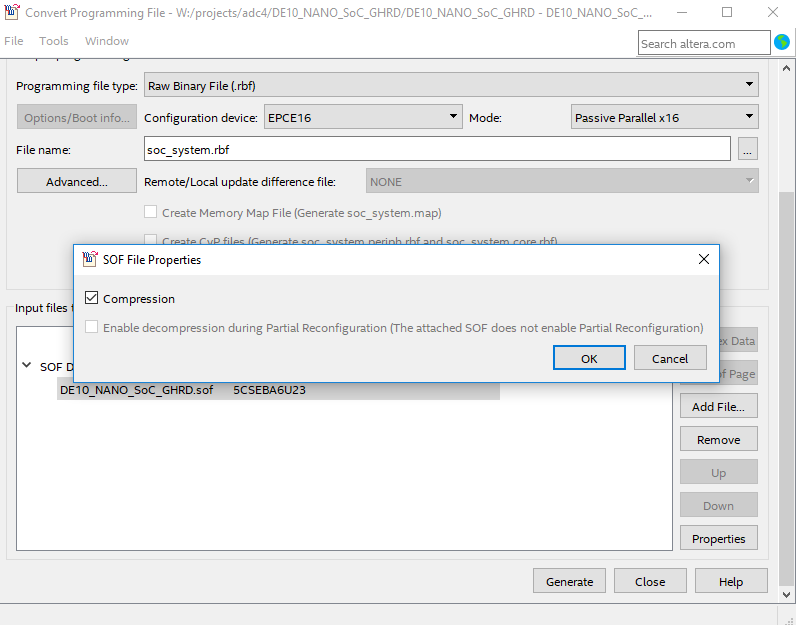

I had the same problem. The reason was the wrong setting in the "Convert Prorgamming File" tool. When you add the SOF file, select the file, then click on "Properties" bottom right. Then click on "Compression". This is how it looks like in Quartus Prime 18.1.:

You also need to set the "Mode" to "Passive Parallel x16". Then save the soc_system.rbf file to the FAT partition on the SD card and u-boot can load it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

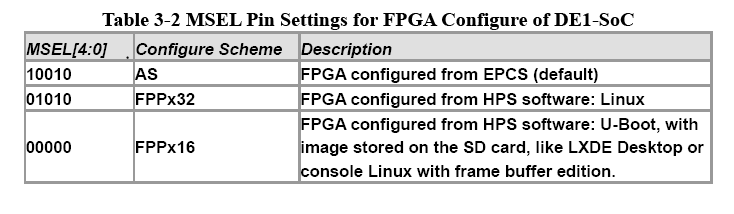

Thanks for the solution provided @FBuss2 . Have been searching this error code for a while. I wish to add on something, the "Mode" is set according to the MSEL pin u set on the DE1-SoC board. You can refer to the table below, the table can be found in DE1-SoC User Manual provided by Terasic, section 3.1 Settings of FPGA Configuration Mode.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page