- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

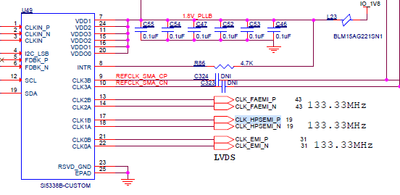

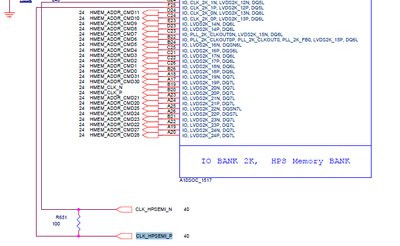

In Arria 10 development kit, CLK_HPSEMI_P/N is provided from Si5338B which is powered by 1.8V. It is provided to 2K bank which is powered by 1.2V(See images below). The supported I/O standards of Si5338B as per datasheet is LVPECL, LVDS(1.8V,2.5V,3.3V), HCSL and CML. What is the IO standard that will be used in Intel Arria 10 to make the signal logically compatible?

1)From Si5338B

To FPGA:

Thanks

Viswa

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Viswa,

Hope you are doing well. Can you please tell me how did you get the value 1.2V in bank 2K? I think the most important thing about signal logic compatibility is the value of the voltage and this case it is find for you to use 1.8V LVDS as your I/O Standard.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the reply.

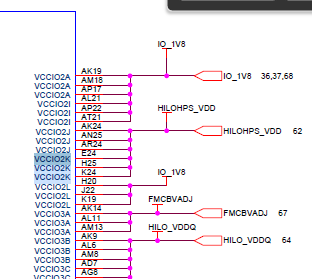

In the Development kit, the 2K bank is powered by the voltage needed for DDR version. If we use DDR4, then it will be powered by 1.2V. From the below image, HILOPHPS_VDD is powering the 2K bank. Also 2K bank is used for interfacing DDR. I have attached the development kit with this question.

Page no 62: HILOHPS_VDD is generated(it powers 2K bank)

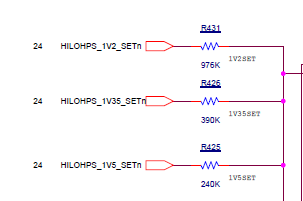

These will set the HILOHPS voltage to either 1.2V,1.35V or 1.5V

In the development kit, there is a voltage mismatch between Clock generator Si5338B and Intel Arria 10 FPGA. Hence these two can't be logically compatible. What IO standard can then be used to make it logically compatible?

Thanks

Viswa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Viswa,

The voltage need to be the same to make it compatible. Thus, if you use 1.2V,1.35V or 1.5V on the other device then your Arria 10 need to use the same voltage as I/O standard followed by requirement based on the guideline.

Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page