- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am designing Linux OS for our Custom board which took design reference from Arria 10 SoC.

I have designed uboot binary image by taking reference from

https://rocketboards.org/foswiki/Documentation/A10GSRDGeneratingUBootAndUBootDeviceTree

and selected QSPI flash for booting the uboot image.

After loading the uboot and peripheral rbf image in the QSPI flash card , it was observed that the HPS is not booting, their is no output on console window , also the debug uart pin is not toggled.

Also, the nRST pin which is used for warm reset becomes low after continuous intervals for around 55usec .

I am unable to understand whether this reset in generated internally by reset manager (in uboot source code ) and if so how to handle this reset so that the HPS is able to boot??

Thanks and Regards,

Priya

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know which Quartus version that you are using?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using Quartus 17.1 version. And for the above query which I posted, I read the manuals and did some changes in our I/O muxing. I configured Dedicated I/O bank UART as the debug UART and now console is showing output.But in the message DDR calibration is getting failed.

The uart console is showing following Error:

U-Boot 2014.10 (Sep 17 2019 - 15:11:16)

CPU : Altera SOCFPGA Arria 10 Platform

BOARD : Altera SOCFPGA Arria 10 Dev Kit

I2C: ready

DRAM: WARNING: Caches not enabled

SF: Read data capture delay calibrated to 1 (0 - 2)

SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiB

FPGA: Early Release Succeeded.

SF: Detected N25Q1024A with page size 256 Bytes, erase size 4 KiB, total 128 MiBemif_reset interrupt acknowledged

emif_reset interrupt acknowledged

emif_reset interrupt acknowledged

Error: Could Not Calibrate SDRAM

DDRCAL: Failed

INFO : Skip relocation as SDRAM is non secure memory

Reserving 2048 Bytes for IRQ stack at: ffe3a6e8

DRAM : 0 Bytes

data abort

pc : [<ffe001cc>] lr : [<ffe02491>]

sp : ffe3fff0 ip : 00000016 fp : 00000001

r10: ffd02078 r9 : ffe3aee8 r8 : ffe00000

r7 : ffe1d3c4 r6 : 00000000 r5 : 00000000 r4 : ffeff000

r3 : ffe3afaf r2 : ffe40000 r1 : ffe3d000 r0 : ffe3aee8

Flags: nzcv IRQs on FIQs on Mode SVC_32

Resetting CPU ...

resetting ...

Could you please help with the error?

Thanks,

Priya

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am unsure why the SDRAM is not calibrated properly, may I know which manual you are following to change these settings?

Please follow these steps to boot the Arria 10 SoC board via QSPI here, which also shows the expected output of the uboot:

https://rocketboards.org/foswiki/Documentation/A10GsrdQspiBootLTS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello ,

I am following the same manual for QSPI boot , provided by rocketboard.

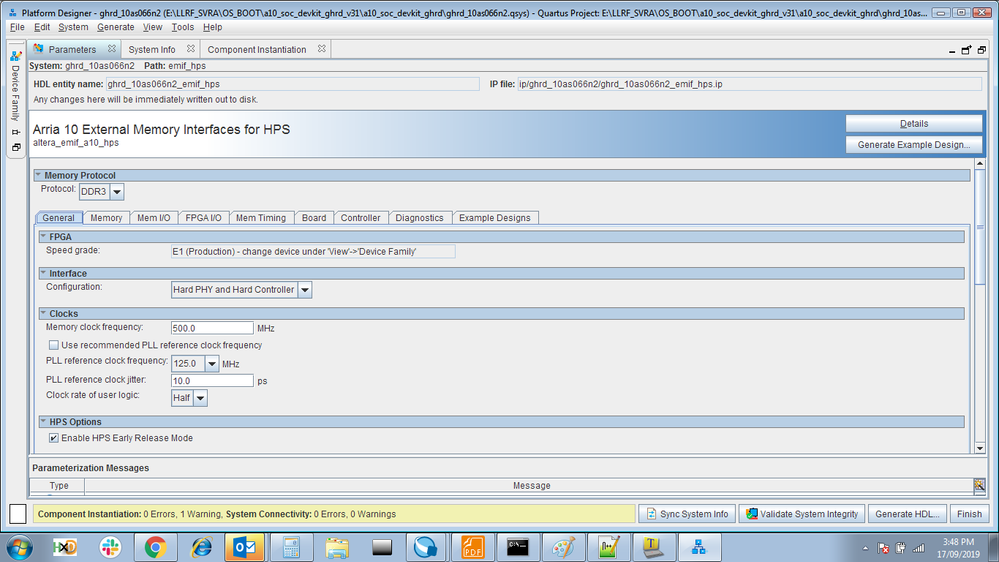

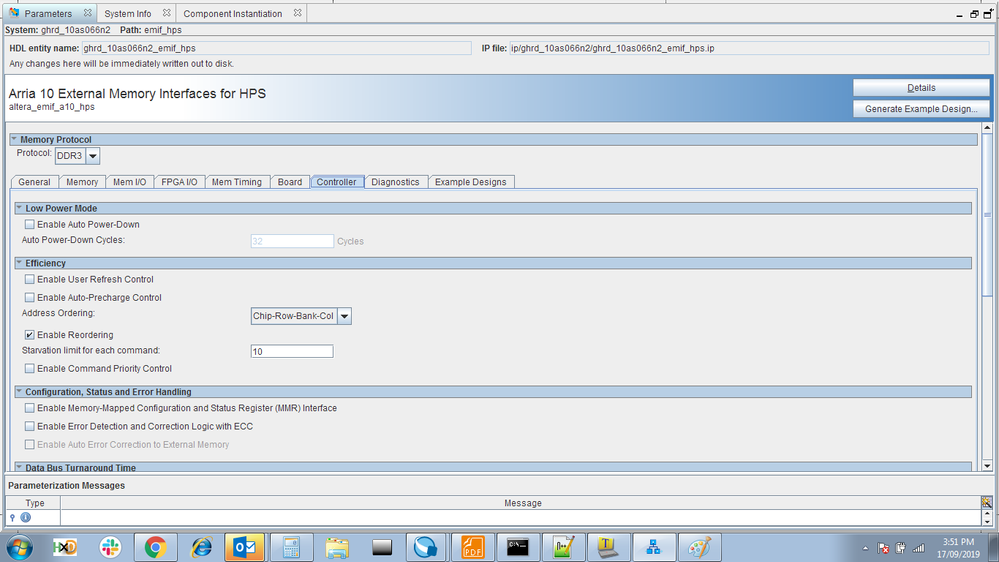

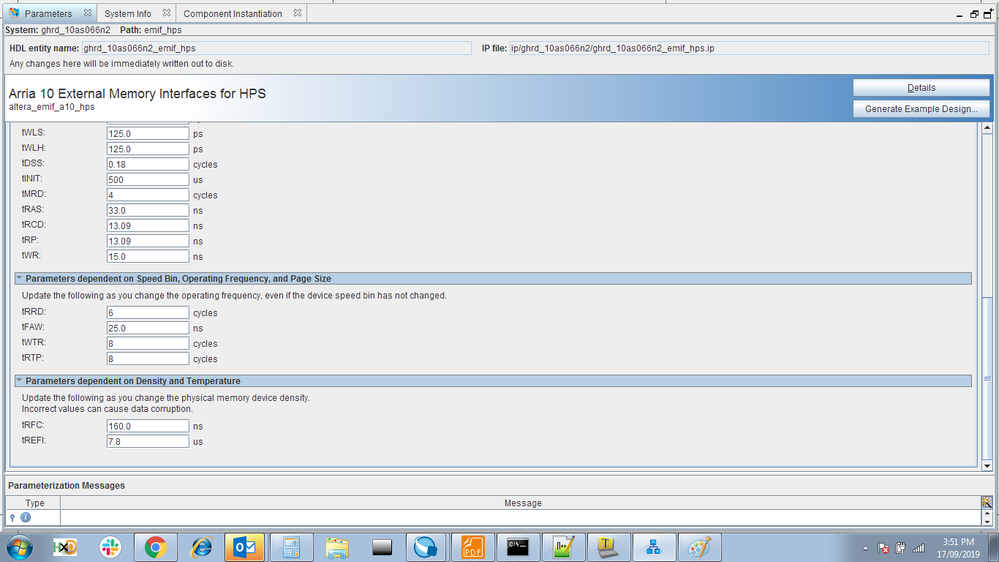

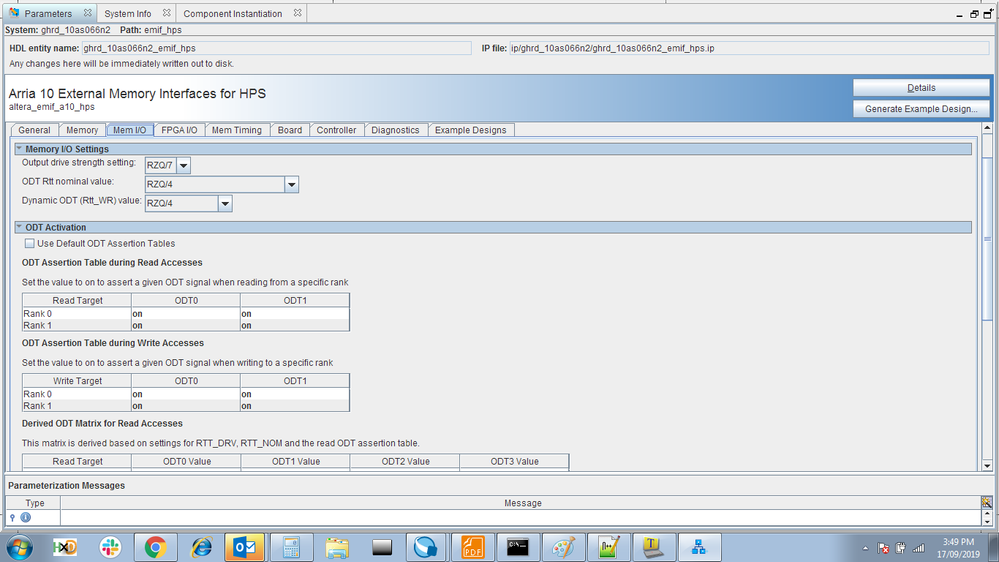

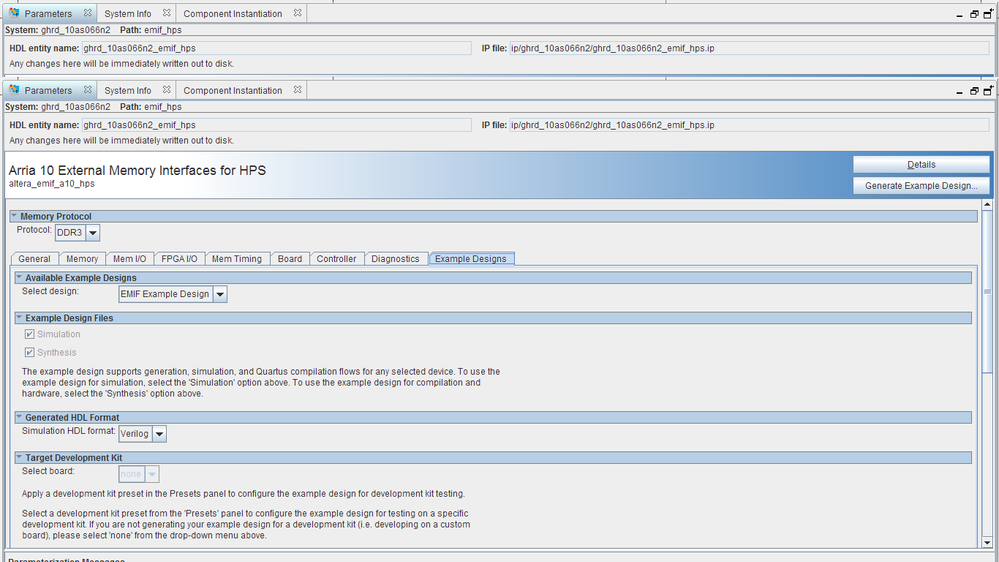

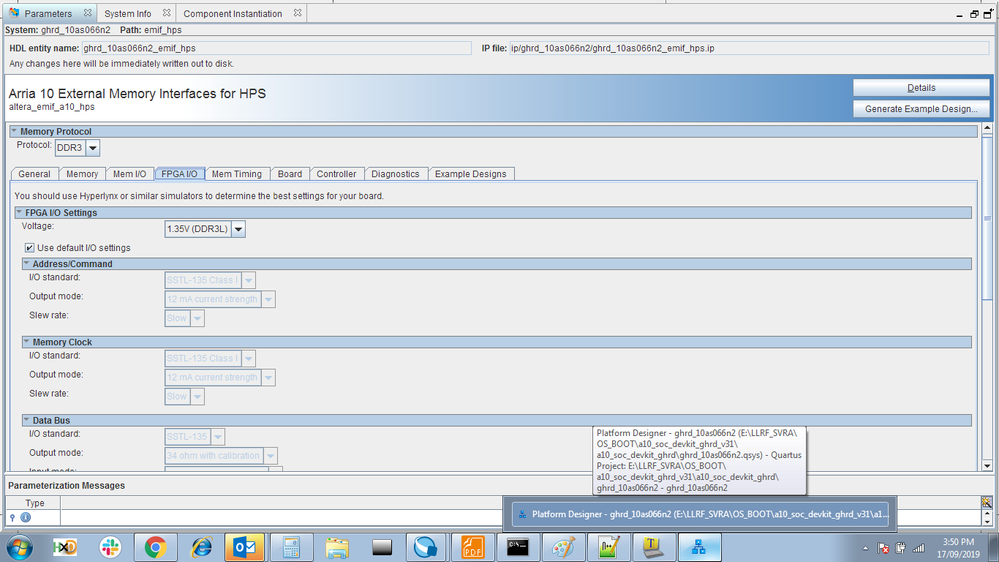

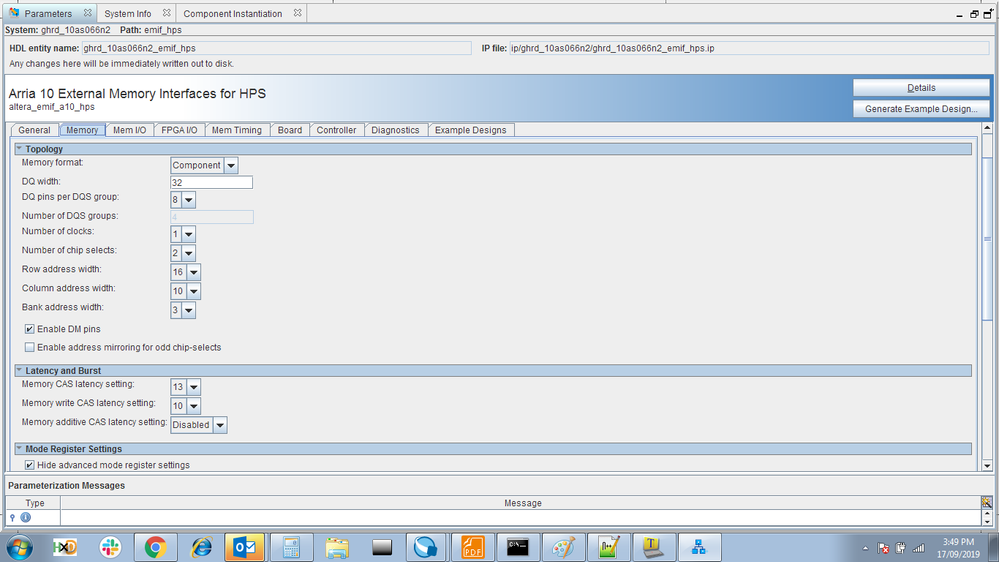

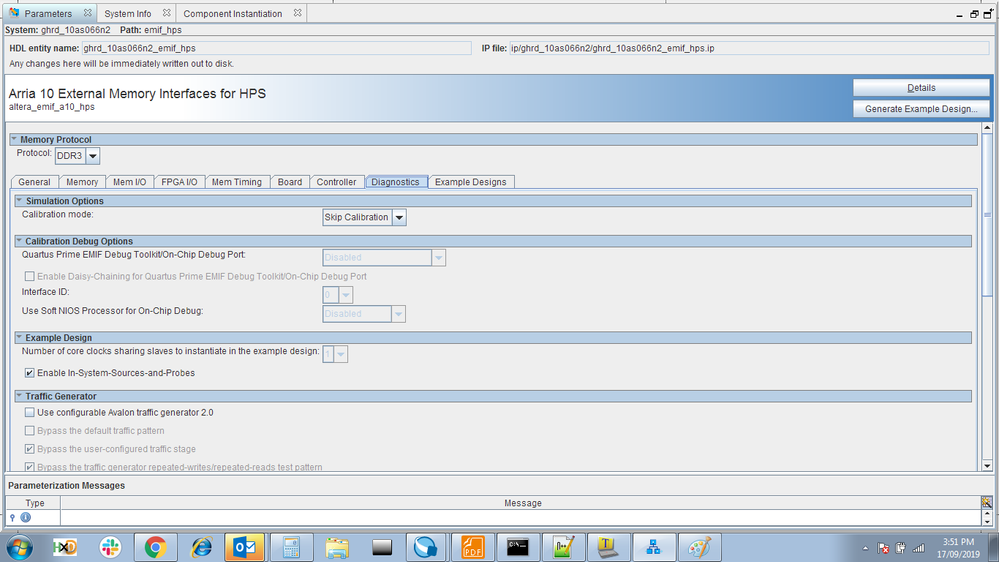

In the GHRD , DDR4 is calibrated at HPS side, and in our custom board, we are using DDR3 at HPS side for calibration. In the Quatus Tool (17.1 version) , we replaced DDR4 with DDR3(MT41K512M16HA-107) at emif_hps interface attached below:

Please help with above query.

Thanks,

Priya

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Priya,

I would like to know if the DDR Timing Paramaters settings made in Quartus in your previous post have fixed this issue.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page