- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

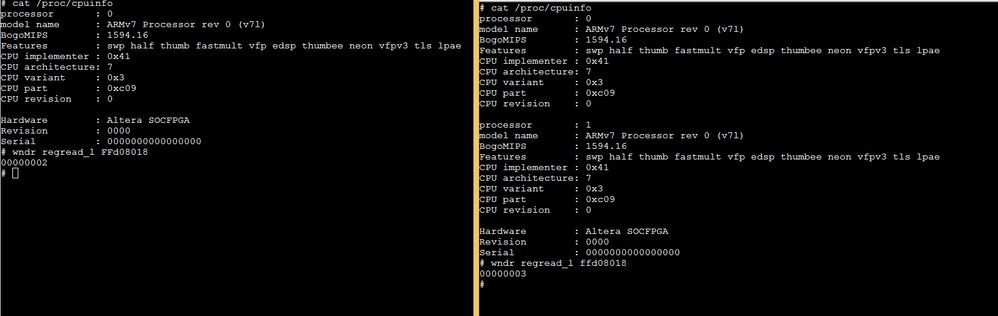

We use cyclone V 5CSEBA5U2317S for a long time and we are sure it has a single core in MPU, it can be confirmed by cat /proc/cpuinfo (shows only cpu0) and register 0xFFD08018 (bit 0 indicates that cpu1 is not available). But we notice that the latest 5CSEBA5U23I7S we bought have dual core inside. Both FPGAs are running the same firmware but on a slightly different versions of boards. Is there any pin on HPS that can block CPU1 or does Intel give an extra core for free on Cyclone V?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

All Cyclone V SoC devices are dual core, using the same Cortex A9. Where are you seeing that this particular device is single core? CPU1 has to be enabled during the boot process, so maybe you never did that.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your quick reply. Here are the links that I found in product detail, basically these two SoC are the same but 5CSEBA5U23I7 says it has 2 processor cores while the one with S says it has 1. Also the price of these 2 are different.

https://www.intel.com/content/www/us/en/programmable/products/general/selector/product-detail.html?partNumber=5CSEBA5U23I7S

https://www.intel.com/content/www/us/en/programmable/products/general/selector/product-detail.html?partNumber=5CSEBA5U23I7

Based on the Cyclone V specification (page 12 in the following link) S indicates it is a single core version.

https://www.mouser.dk/datasheet/2/612/cv_51001-1098989.pdf

We are always using 5CSEBA5U23I7S and by reading LSB of sysmgr register (0xFFD08000) we can see cpu 1 is not available (bit set to 0) in MPU in our older 5CSEBA5U23I7S. But in our recent purchased 5CSEBA5U23I7S the bit is set to 1 meaning that CPU1 is available in MPU.

We are running exactly the same firmware image (same uboot, same linux and same FPGA) so how come only the newer FPGAs enables the CPU1 not the old ones?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've been working with these devices for 6 years and never knew there was a single core option. I guess CPU1 is simply not available in devices with the S code. Is your question that you have newer S code devices that now show both cores available?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yeh exactly ... all the older S devices (bought more than 2 years ago) we got here has only CPU 0 core but the most recent S devices we bought shows CPU0 and CPU1 are all there. I am also confused because we have been using this single core FPGA since 2014 because it is much cheaper than the dual core. The only difference we can see on the chip is that the dual core FPGAs are made in Taiwan while the single core FPGAs are made in Korea....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Correct me if I am wrong, the newly ordered 5CSEBA5U23I7S(which is a single core) devices shows both cores available (CPU0 and CPU1)?

But the old 5CSEBA5U23I7S devices that you have owned, shows only one core available(CPU0)?

May I know if you are you facing any booting issues with this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes you are right.

I don't have booting issue with 2 cores available.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the information, I will check with our internal team regarding this issue.

Is it possible for you to share the screenshot of the "LSB of sysmgr register (0xFFD08000) we can see cpu 1 is not available (bit set to 0) in MPU", for both old and new devices?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry the address 0xFFD08000 is not right. I forgot to mention the offset. The correct address is 0xFFD08018 which is shown in picture above.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

Thanks for the screenshot, I will check with our internal team regarding this issue.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I would like to know if all your questions have been answered.

"Is there any pin on HPS that can block CPU1 or does Intel give an extra core for free on Cyclone V?"

-> Are you using Linux? You can disable the cpu 1 (even though it is not available) by root:

echo 0 > /sys/devices/system/cpu/cpu1/online

Hope this helps.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using Linux and actually we are doing this <echo 0 > /sys/devices/system/cpu/cpu1/online> to disable CPU1.

But what we are more interested in is why the two FPGAs we bought are different even serial numbers are the same.

And do we still get 2 cores with 5CSEBA5U23I7S FPGAs in the future? Because we are going to buy more.

If so, can we use the second core safely?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am still waiting for internal team to reply, can you specify how many board are involved/affected?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We bought at least three hundreds of 5CSEBA5U23I7S (both old and new) and we are going to buy more. So far we checked around 50 of them. All older ones has single core and newer ones have due core.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you execute "lscpu" in Linux to display the info on the new and old device?

Is it possible to share the screenshot as well?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We don't have "lscpu" command in our customized Linux. We only have /proc/cpuinfo which should show similar info.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is there any way you could check the core count of the device from your customized Linux?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Isn't /proc/cpuinfo enough? If not we can try to integrate lscpu

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Besides cpuinfo here is dmesg info in our system, the following one shows the system found 2 cores:

# dmesg

Booting Linux on physical CPU 0x0

Initializing cgroup subsys cpuset

Linux version 3.10.31-ltsi (deva@deva-desktop) (gcc version 4.9.3 (Buildroot 2015.11-ga9b17cc-dirty) ) #3 SMP Mon Nov 18 09:11:44 CET 2019

CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=10c5387d

CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

Memory policy: ECC disabled, Data cache writealloc

On node 0 totalpages: 131072

free_area_init_node: node 0, pgdat 80961840, node_mem_map 8099f000

Normal zone: 1024 pages used for memmap

Normal zone: 0 pages reserved

Normal zone: 131072 pages, LIFO batch:31

PERCPU: Embedded 8 pages/cpu @80dab000 s10688 r8192 d13888 u32768

pcpu-alloc: s10688 r8192 d13888 u32768 alloc=8*4096

pcpu-alloc: [0] 0 [0] 1

Built 1 zonelists in Zone order, mobility grouping on. Total pages: 130048

Kernel command line: console=ttyS0,115200 root=/dev/mtdblock1 rw rootfstype=jffs2

PID hash table entries: 2048 (order: 1, 8192 bytes)

Dentry cache hash table entries: 65536 (order: 6, 262144 bytes)

Inode-cache hash table entries: 32768 (order: 5, 131072 bytes)

Memory: 512MB = 512MB total

Memory: 509792k/509792k available, 14496k reserved, 0K highmem

Virtual kernel memory layout:

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xfff00000 - 0xfffe0000 ( 896 kB)

vmalloc : 0xa0800000 - 0xff000000 (1512 MB)

lowmem : 0x80000000 - 0xa0000000 ( 512 MB)

modules : 0x7f000000 - 0x80000000 ( 16 MB)

.text : 0x80008000 - 0x80523014 (5229 kB)

.init : 0x80524000 - 0x809319c0 (4151 kB)

.data : 0x80932000 - 0x80964810 ( 203 kB)

.bss : 0x80964810 - 0x8099ebec ( 233 kB)

SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

Hierarchical RCU implementation.

NR_IRQS:16 nr_irqs:16 16

sched_clock: 32 bits at 100MHz, resolution 10ns, wraps every 42949ms

Console: colour dummy device 80x30

Calibrating delay loop... 1594.16 BogoMIPS (lpj=7970816)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 512

CPU: Testing write buffer coherency: ok

ftrace: allocating 14872 entries in 44 pages

CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

Setting up static identity map for 0x803b5fa0 - 0x803b5fd4

CPU1: Booted secondary processor

CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

Brought up 2 CPUs

SMP: Total of 2 processors activated (3188.32 BogoMIPS).

CPU: All CPU(s) started in SVC mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here is the Dmesg log from single core FPGA:

Booting Linux on physical CPU 0x0

Initializing cgroup subsys cpuset

Linux version 3.10.31-ltsi (deva@deva-desktop) (gcc version 4.9.3 (Buildroot 2015.11-ga9b17cc-dirty) ) #2 SMP Fri Oct 4 14:40:33 CEST 2019

CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=10c5387d

CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

Machine: Altera SOCFPGA, model: Altera SOCFPGA Cyclone V

Memory policy: ECC disabled, Data cache writealloc

On node 0 totalpages: 131072

free_area_init_node: node 0, pgdat 80973840, node_mem_map 809b1000

Normal zone: 1024 pages used for memmap

Normal zone: 0 pages reserved

Normal zone: 131072 pages, LIFO batch:31

PERCPU: Embedded 8 pages/cpu @80dbd000 s10688 r8192 d13888 u32768

pcpu-alloc: s10688 r8192 d13888 u32768 alloc=8*4096

pcpu-alloc: [0] 0 [0] 1

Built 1 zonelists in Zone order, mobility grouping on. Total pages: 130048

Kernel command line: console=ttyS0,115200 root=/dev/mtdblock1 rw rootfstype=jffs2

PID hash table entries: 2048 (order: 1, 8192 bytes)

Dentry cache hash table entries: 65536 (order: 6, 262144 bytes)

Inode-cache hash table entries: 32768 (order: 5, 131072 bytes)

Memory: 512MB = 512MB total

Memory: 509720k/509720k available, 14568k reserved, 0K highmem

Virtual kernel memory layout:

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xfff00000 - 0xfffe0000 ( 896 kB)

vmalloc : 0xa0800000 - 0xff000000 (1512 MB)

lowmem : 0x80000000 - 0xa0000000 ( 512 MB)

modules : 0x7f000000 - 0x80000000 ( 16 MB)

.text : 0x80008000 - 0x80523014 (5229 kB)

.init : 0x80524000 - 0x809439c0 (4223 kB)

.data : 0x80944000 - 0x80976810 ( 203 kB)

.bss : 0x80976810 - 0x809b0bec ( 233 kB)

SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

Hierarchical RCU implementation.

NR_IRQS:16 nr_irqs:16 16

sched_clock: 32 bits at 100MHz, resolution 10ns, wraps every 42949ms

Console: colour dummy device 80x30

Calibrating delay loop... 1594.16 BogoMIPS (lpj=7970816)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 512

CPU: Testing write buffer coherency: ok

ftrace: allocating 14872 entries in 44 pages

CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

Setting up static identity map for 0x803b5fa0 - 0x803b5fd4

CPU1: failed to come online

Brought up 1 CPUs

SMP: Total of 1 processors activated (1594.16 BogoMIPS).

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page