- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi 您好,

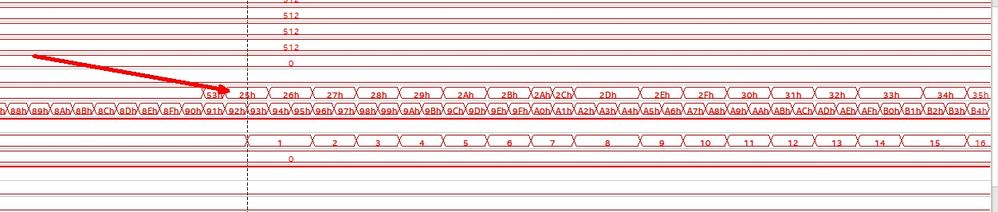

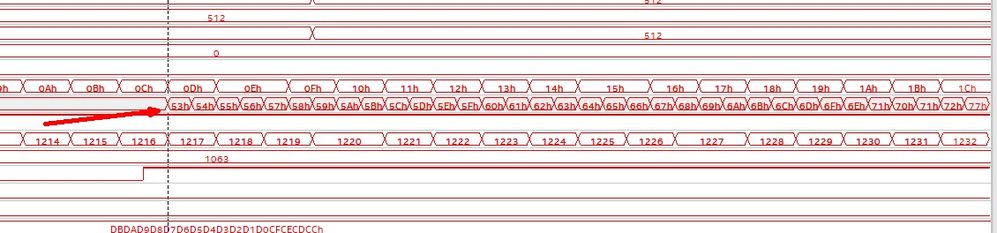

客户在使用C10GX,10CX105,DDR3L读取测试中,发现读出的数虽然是对的,但是和写入的数地址上有偏移,位置对不上。每次上电的偏移,都不一样。现象如下图所示:能否帮助分析一下,现象。

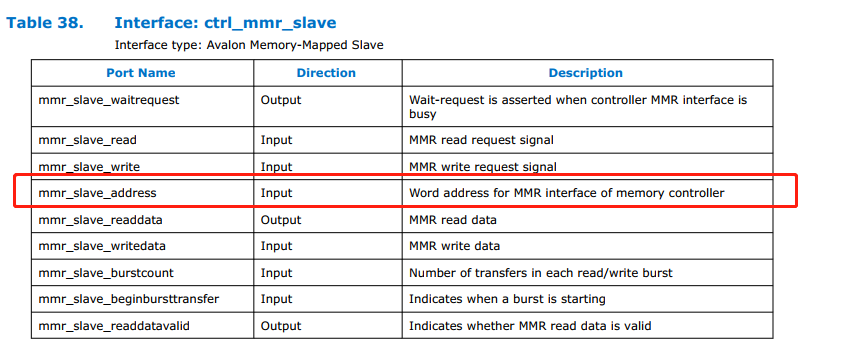

在DDR3 手册中,有如下描述,写入的时候,是按照字写的,但是没有见到是按照字读还是字节读,想确认下。

Ted.Gao

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ted,

Is it possible to share your design or sharing the steps so that I can help to reproduce the issue locally?

Thanks

Regards,

Aida

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NuraidaA,

the design was attached. FYI

Quartus 18.1 Pro

Ted

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ted,

I checked your design and I can see that you are using 150Mhz (half rate) on emif clk. Is it the similar frequency used in your sampling clock in signal tap?

Anyway, sometime time shift is due to the signaltap. As in you are using same frequency on both clk, so it might accidentally shifted. But, if your are not seeing any error/problem then there is nothing to worry about.

I recommend using higher frequency at your sample clock but please make sure it able to close timing.

Thanks

Regards,

Aida

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page