- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi everyone,

I am currently using Cyclone V 5CSEMA5F31C6NF device to design a testbench, with PLL being used.

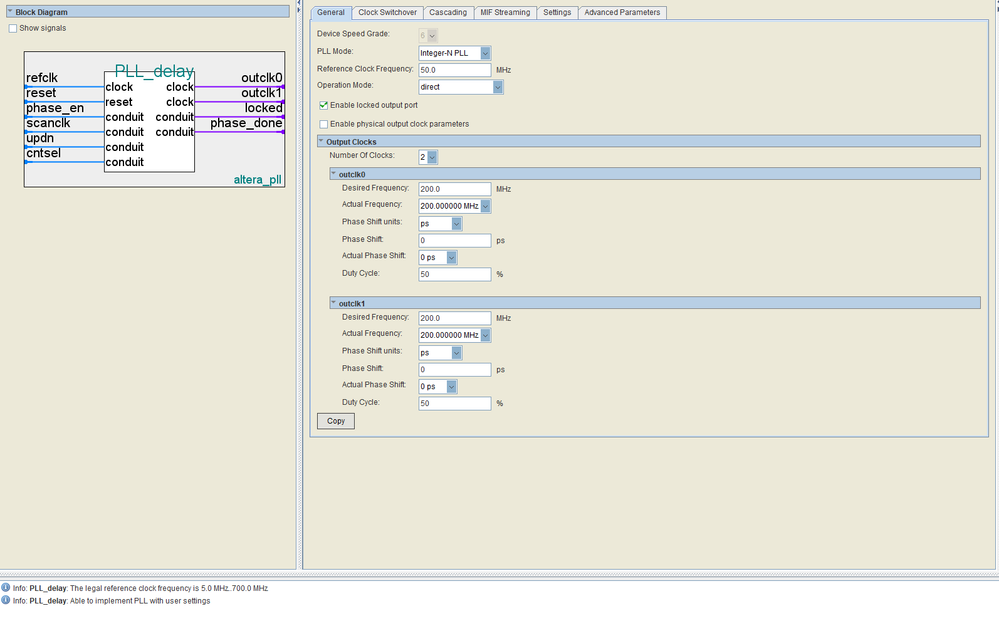

I want to perform dynamic phase shift operation on this PLL and so I set its parameters as shown in the picture below.

However, when I analyse and synthesis the verilog design which I have put at the end of this post for your reference, I got warnings as follows:

Warning (10034): Output port "clkout[0]" at altera_cyclonev_pll.v(637) has no driver

Warning (10034): Output port "loaden" at altera_cyclonev_pll.v(641) has no driver

Warning (10034): Output port "lvdsclk" at altera_cyclonev_pll.v(642) has no driver

I have checked document " Implementing Fractional PLL Reconfiguration with

Altera PLL and Altera PLL Reconfig IP Cores", "IOPLL Intel® FPGA IP Core User Guide" and "ALTPLL (Phase-Locked Loop) IP Core User Guide", but could not find out reasons. Documentation about dynamic phase shift here is also ambiguous, it just mentions examples and explains functions of each ports but not enough details.

If anyone has done dynamic phase shift with I/O PLL using ordinary altera PLL IP (not reconfiure pll ip), could you please kindly offer help for this?

A side question is, may I ask the purpose of logical counter selection port "cntsel" in dynamic phase shift PLL? Is it to change VCO's crystal's oscillator to shift the phase to 1/8 of the changed frequency or something else? (Documentation here is also vague...)

Thank you very much!

Best Wishes,

Mingqiang

module Clock_source(clk_in,clk_out,

clk_shift,reset,shift_dir,

counter_sel,phase_done,locked,phase_en);

input wire clk_in,reset,shift_dir,phase_en;

output wire clk_out,clk_shift,phase_done,locked;

input wire[4:0] counter_sel;

PLL_delay PLL_source(.refclk(clk_in), .rst(reset),

.locked(locked), .outclk_0(clk_out), .scanclk(clk_out),

.outclk_1(clk_shift), .updn(shift_dir), .cntsel(counter_sel),

.phase_en(phase_en), .phase_done(phase_done));

endmodule

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Mingqiang

The dangling output port is based on the operation mode, usage setting and explicit connection that we have implemented. The purpose of logical counter usage can be found here:

Thanks.

Eng Wei

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page