- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

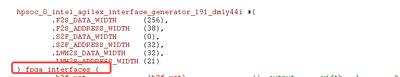

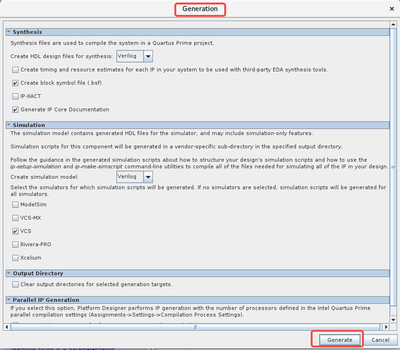

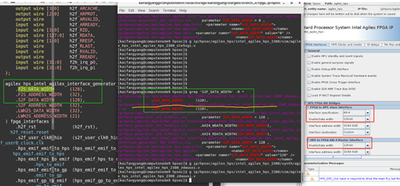

Generate Verilog for Simulation of HPS, But S2F_DATA_WIDTH always 0, mismatch with Setting of HPS. Why or How to solve this mismatch. Thanks

Please see the following picture.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You should be looking for H2F, not S2F, as the port to connect to. Can you show more of the parameter settings and code?

Not sure what device you are using, but "S" I think is the connection to the hardened SDRAM controller in Cyclone V and Arria V SoC (it's been a while since I've looked at them).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

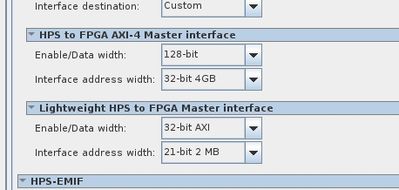

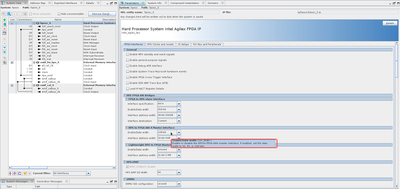

The parameter setting as following picture.

Code:

Simulation Report Error:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Are you getting any error during compilation in Quartus?

Which file in your project did you check that stated the value is 0?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have got no errors during compilation,(Quartus prime pro eition 22.2).

I also send you my project file(please check the attachment) ,you can open project in your local place. please help me double check.

Which file in your project did you check that stated the value is 0?

answer: you can grep the fpga_interfaces in your generation IP file. because different generation, maybe different file names, but instantiation name is always fpga_interface.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please see the attachment, I have send the whole project. You can open in your local place. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the clarification, let me check on my side.

I am a little bit tight up on my side a the moment, thus it might take a few days.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you so much. No problem. Waiting for you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Are you familiar with the Platform Designer?

Also, I am not exactly sure how it got the value as you mentioned, I tried to do the same settings as you did but I do have the value according to what was set in the HPS IP.

Value: 1,2,3 = drop down selection from Top to Bottom, with 0 being unused.

My guess would be, that you had no connection with the H2F interconnect, despite it being enabled or you might have not re-generate it after you had set it.

Anyway, we always recommend customer to go from our GHRD and build/remove any peripherals etc., of their own design from there. The GHRD is based of our dev kit, for you it will be the Agilex 7 SoC Dev Kit:

https://www.rocketboards.org/foswiki/Documentation/AgilexSoCGSRD

https://github.com/altera-opensource/ghrd-socfpga

You can view how the GHRD interconnects are and use the GHRD. Are you okay with proceeding with the GHRD? If not, you could try to create a new .qsys and add all new IPs as per the GHRD that you would want to work/play around with then try again.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

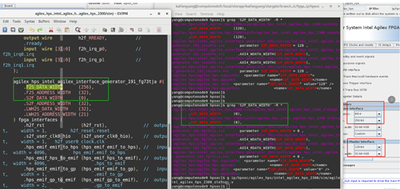

Linux Quartus version : Quartus Prime Verison 22.4.0 Build 94

Agilex FPGA AGFB027R25A****

Hi,

After many attempts, I encountered a very strange phenomenon.

Please check my IP configuration options.

option 1:

When I configure F2H data width 128 and H2F data width 128(max), Compile the generated verilog ip file to find the data bit width parameter is normal 128.

option 2:

When I configure F2H data width 256 and H2F data width 128(max), Compile the generated verilog ip file and find that the F2S data bit width parameter is normal 256, but the S2F data bit width parameter is wrong 0.

Option 1 & option2 only the F2H bit width parameter was modified.

We may need to set the F2H bit width parameter 256, but we cannot solve the problem of setting the S2F bitwidth parameter to 0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you tired to remove the HPS IP and add a new one a re-generate?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, try to generate one, then found above phenomenon.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am still not seeing what you are seeing.

Can you list all the settings/changes you made once you select the HPS Agilex IP from the IP catalog to Generating the HDL in Platform Designer:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Please see my whole project.

BTW: Whether it's license problem or not?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I doubt it is a licensing issue, yes I am working from your project that I am not seeing the issue, with just removing and re-adding the HPS IP, I can see all the config changes respectively.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

On a fresh Platform Designer, after creating a new .qsys file, can you share the whole steps you did from adding the IP to any changes, connections, export etc. that you did. We need the full list since I am not seeing the issue what you seeing.

As a matter of fact, please see how our GHRD connection is done:

https://www.rocketboards.org/foswiki/Documentation/AgilexSoCGSRD

What is your objective that you made such connection anyway? We recommend that you use the GHRD and you may remove any unwanted IPs or change an default settings then proceed from there.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please check on my previous respond.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you so much, I am checking, will tell you when we have result.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any new update?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I hope you have update for this week. Let me know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry, I still can't get the right confiuration for simulation.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page