- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Despite making changes inside Qsys in regards to switching desired unused pins to LOANIO from regular GPIO, exporting the new HPS LOAN IO signals, and generating new preloader files, I still cannot get the desired output from these pins. I'm confident in the VHDL design itself being correctly set up. When measuring the pins voltage with an Oscilloscope they are set 'high' and seem to remain unresponsive to any logic I set them too. Could their possibly be anything I'm missing? I've looked at almost every piece of documentation I could have and every community post that even remotely mentions LOAN IO but I still seem to be unable to get them working. Any help is appreciated.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Which device? How are you making the connections? What do your settings look like in the HPS parameter editor? I think more details are needed here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I agree and thanks for the comment.

Device: Cyclone V

How I am making the connections within design:

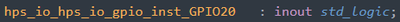

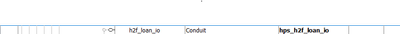

Top level pin being targeted, this signal is mapped to one of the physical FPGA pins:

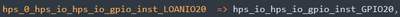

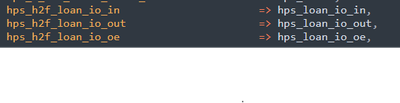

The exported LOANIO20 signal within Qsys block is being mapped directly to top level pin as per documentation:

The exported hps_loan_io_oe for LOANIO20 is set to a '1' to enable it being an output and i'm trying to output a '0' to the top level pin:

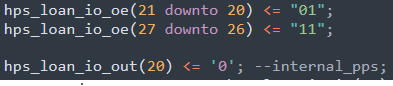

The settings for my HPS parameter editor are as follows:

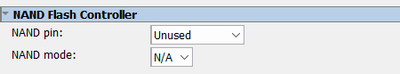

These NAND pins are set to Unused to allow for LOANIO accessibility per documentation

LOANIO Signals within Qsys are being exported

I am unsure if there is more information within QSYS or the HPS parameter editor that may be useful for me to include in order to solve this issue, please let me know!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your export name in Platform Designer (hps_h2f_loan_io) doesn't match your code so there's no connection there. You should be seeing warnings about that. Check the template in the Generate menu in Platform Designer to make sure you instantiate and connect correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Oh yes sorry, I forgot I gave them different signal names when instantiating the Qsys block.

This should clear things up, thats my bad for not including this in the first reply.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Are you still having issues?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The mux table still shows the NAND interface bold for the pins you set as loaner I/O. Is the NAND controller disabled? You would get a conflict warning I would think.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The NAND interface is not being used, and there are no conflict warnings in that regard.

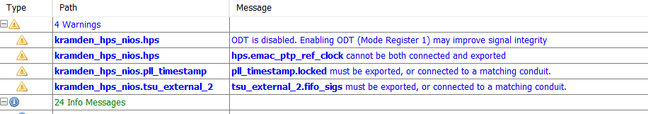

These are the warnings I have, I do no think they are related to this issue but i hope im wrong.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share your design, I would like to see the settings from my side.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any update from your side?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Hope you have new updates, please check my previous responses.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page