- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What we have is a self designed board that uses the Max 10 and the rest of the peripherals almost match the 10M50 evaluation board. The self designed board does not receive power from the Laptop/ PC and so we are unsure if the board is being detected by in the program upload process at all, because Quartus only says "Program failed" when we tried to upload it. The same procedure, JTAG cable and program were followed for the Evaluation Kit and it worked perfectly.

can we a. find a solution to checking if the JTAG hardware is faulty on the board

b. The burning process should differ in a newly design, non proprietary board?

c. any other reason as to why the software might not upload?

Any and all suggestions appreciated!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

- Check the FPGA part number, Is it same?

- Are you able to “auto-detect” to detect the physical device in the JTAG chain?

- Check the status of nCE,nCONFIG and nSTATUS pins.

- Check pull-up/pull-down resistors and also check the soldering contact.

- Check the power supplies are ramped up to the appropriate voltage level according to the POR requirements. Refer below link for POR.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_pwr.pdf

Attached some image on error message and pin status.

For Configuration troubleshooting refer below link.

https://www.intel.com/content/www/us/en/programmable/support/support-resources/support-centers/devices/cfg-index/fpga-configuration-troubleshooter.html

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey, thanks for your response! Some follow up questions inline with your questions:

Check the FPGA part number, Is it same?

>> yes, 10M08 Evaluation Kit and 10M08E144 has been used in the designed board as well.

Are you able to “auto-detect” to detect the physical device in the JTAG chain?

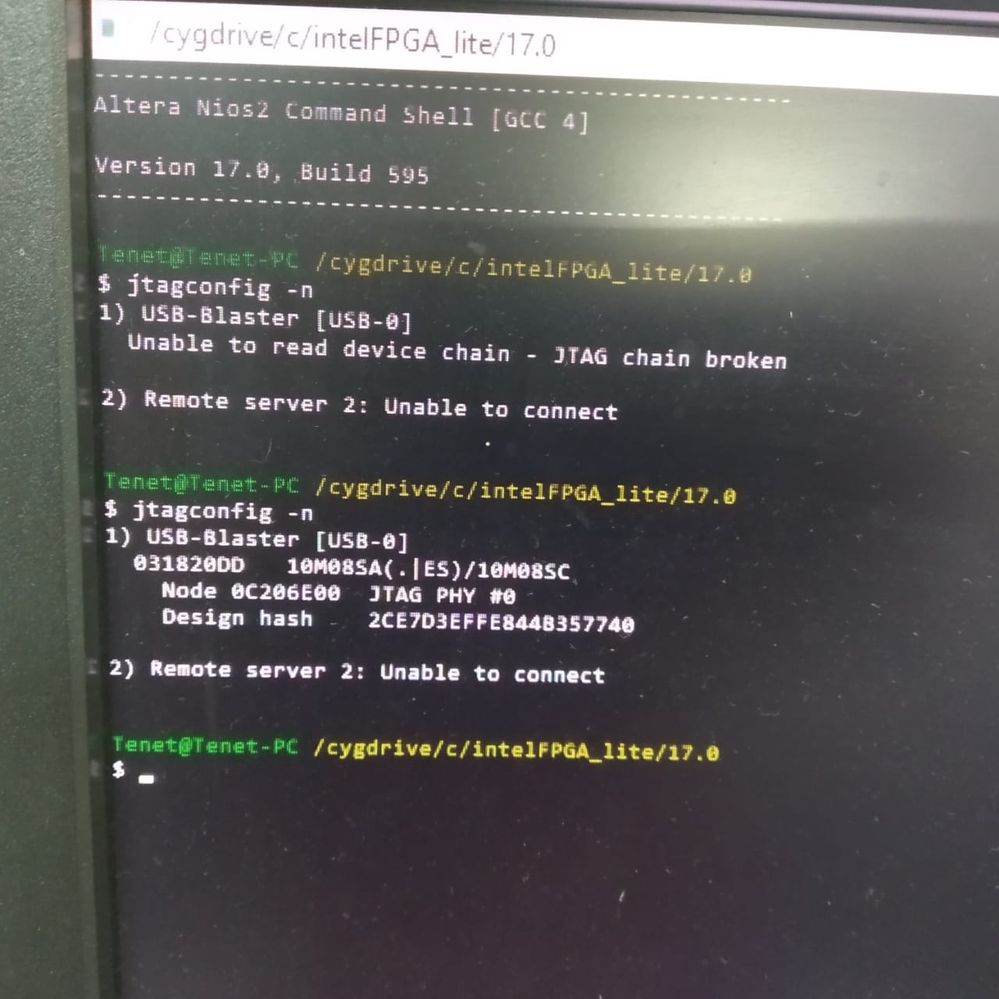

>> NO, check out the image attached at the end.

Check the status of nCE,nCONFIG and nSTATUS pins.

>> CAN WE GET A REFERENCE MANUAL FOR THE 10M08 EVAL KIT? WHAT IS THE EXPECTED OUTPUT FOR THESE PINS WHEN JTAG CHAIN IS PROPERLY DETECTED?

Check pull-up/pull-down resistors and also check the soldering contact.

>> FOR WHICH I/O PORT?

Check the power supplies are ramped up to the appropriate voltage level according to the POR requirements. Refer below link for POR.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_pwr.pdf

>> Could you help by providing us with a schematic diagram? Where are the test pins/ pads available in the Evaluation Board at least?

Attached some image on error message and pin status.

>>

I'd be very grateful for any links on testing and debugging these problems, thank you!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am realy confused,

Are you using self designed board? or Max 10 Evaluation board?

please check the Configuration troubleshooting refer below link.

https://www.intel.com/content/www/us/en/programmable/support/support-resources/support-centers/devices/cfg-index/fpga-configuration-troubleshooter.html

Are you able to “auto-detect” to detect the physical device in the JTAG chain?

>> NO, check out the image attached at the end.

>>>I can see 10M08SA and 10M08SC , is it for Max 10 Evaluation board

Check the status of nCE,nCONFIG and nSTATUS pins.

>> CAN WE GET A REFERENCE MANUAL FOR THE 10M08 EVAL KIT? WHAT IS THE EXPECTED OUTPUT FOR THESE PINS WHEN JTAG CHAIN IS PROPERLY DETECTED?

>>> you can find the information from from configuration user guide or from pin connection guidelines

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_config.pdf

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/dp/max-10/pcg-01018.pdf

Check pull-up/pull-down resistors and also check the soldering contact.

>> FOR WHICH I/O PORT?

>>>FPGA Configuration pins(PIN connection guidelines) and your board power supply components.

Check the power supplies are ramped up to the appropriate voltage level according to the POR requirements. Refer below link for POR.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_pwr.pdf

>> Could you help by providing us with a schematic diagram? Where are the test pins/ pads available in the Evaluation Board at least?

FPGA pins like VCC, VCCA , VCCIO also configuration pins like TCK,TDI, TMS & nCE,nCONFIG and nSTATUS pins

https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/kit-max-10-evaluation.html

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, sorry for the confusion but we're using BOTH. We need to debug the self designed board and the Eval Board is just for reference.

The Eval Board is being recognized in the JTAG chain but the self designed one is not. Any way to fix the JTAG recognition issue there?

Thank you for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Eval Board is being recognized in the JTAG chain but the self designed one is not. Any way to fix the JTAG

>>It means JTAG chain not working.

May be, device not powered, components not properly connected or defective. Refer pin connection guidelines

please check the FPGA pins like VCC, VCCA , VCCIO also configuration pins like TCK,TDI, TMS & nCE, nCONFIG and nSTATUS pins.

please check the Configuration troubleshooting refer below link.

https://www.intel.com/content/www/us/en/programmable/support/support-resources/support-centers/devices/cfg-index/fpga-configuration-troubleshooter.html

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any update, Have you solved the problem.

Thanks & Regards

Anand

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page