- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

I meet a problem about reading/writing L4 Peripheral Slave Bus on S10 SX Device.

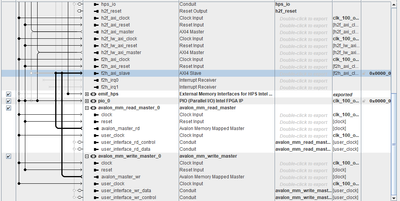

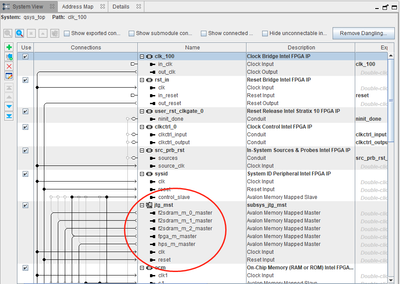

I code avalon_mm_read_master module and avalon_mm_write_master module by myself, and I put them into Platform Designer as Figure 1 shown.

I firstly set the read and write address to DDR address such as 0x7fff0000. Data grabed in SignalTap shows read and write succeed.

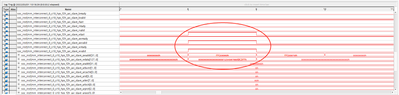

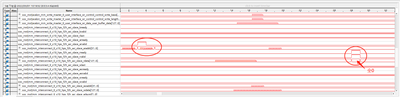

Then I change read and write address to l4 slave peripheral address such as uart(0xffc02000) and gpio(0xffc03000). Data grabed in SignalTap shows in Figure 2 and Figure 3. From figures, the operation that data is written into the exact setting address succeeds, but data read out of the address is all zero, which means data cannot be read/wrote into l4 slave peripheral bus address.

The tools version all I use are 19.1 Pro Quartus Prime, 2017.09 uboot, 4.9.78-ltsi-altera linux, S10 device number is 1sx280lu2f50e2vgs2(Stratix 10 SoC Development Kit, ES Edition).

What I do is I use sdimage in https://releases.rocketboards.org/release/2019.04/gsrd/s10_gsrd/ and I change dtb file which add uart1 with status "okay", also I change the u-boot.scr file like https://rocketboards.org/foswiki/Documentation/S10SGMIIRDV181CreateUbootScript and extra configure some firewall registers of l4 slave peripheral bus. The u-boot.scr is also attached below.

Could you please give me some suggestions what I can do?

Thank you very much!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Anyone can help me?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, we will need sometime to do analysis and get back to you. Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello stanley015,

I’m reviewing your u-boot script attached.

By the way, have you accessed F2H bridge with JTAG Master which is default configuration of S10 SoC GHRD?

Best regards,

Yoshiaki Saito

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Saito,

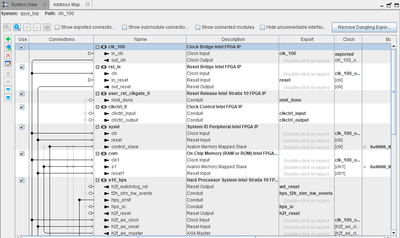

This is my rest of qsys attached.

I build my project regarding to S10 SoC GHRD named "s10_soc_devkit_ghrd_es.tar.gz" which is downloaded in https://releases.rocketboards.org/release/2019.04/gsrd/s10_gsrd/. From the qysy of s10_soc_devkit_ghrd_es.tar.gz, I actually can see the module of jtg_mst.

However, I delete this module from my qsys because I think it will not effect read/write from f2h_axi_slave to l4 slave peripheral bus. I should add this module back or not and what the function of this module is. Also, what I should do after this module is added back?

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hans_1st,

I tried "s10_soc_devkit_ghrd_es.tar.gz" on Stratix 10 SoC Devkit ES, and have confirmed to be able to access HPS periphrals such as UART0.

After booting U-boot, I also executed the following commands.

S10 SoC Bridge Configuration

https://rocketboards.org/foswiki/Documentation/S10SoCBridgeConfiguration

Next, we can access to HPS via “JTAG to Avalon Master Bridge Cores” below in jtg_mst.qsys.

Then, the system-console which is located in intelFPGA_pro/19.1/syscon/bin is launched. This is a debugging tool for “JTAG to Avalon Master Bridge Cores”. See below.

Using System Console

https://rocketboards.org/foswiki/Documentation/GSRDQuartusProgrammer

Type a command below to show all path name of JTAG port in the FPGA system.

The 4th path is for accessing F2H bridge.

% get_service_paths master

{/devices/1SX280LN2S(2|1)|1SX280LN3S1|..@2#1-9.3.2#Stratix 10L SoC Dev Kit/(link)/JTAG/(110:132 v1 #0)/phy_0/master}

{/devices/1SX280LN2S(2|1)|1SX280LN3S1|..@2#1-9.3.2#Stratix 10L SoC Dev Kit/(link)/JTAG/(110:132 v1 #1)/phy_1/master}

{/devices/1SX280LN2S(2|1)|1SX280LN3S1|..@2#1-9.3.2#Stratix 10L SoC Dev Kit/(link)/JTAG/(110:132 v1 #2)/phy_2/master}

{/devices/1SX280LN2S(2|1)|1SX280LN3S1|..@2#1-9.3.2#Stratix 10L SoC Dev Kit/(link)/JTAG/(110:132 v1 #3)/phy_3/master} {/devices/1SX280LN2S(2|1)|1SX280LN3S1|..@2#1-9.3.2#Stratix 10L SoC Dev Kit/(link)/JTAG/(110:132 v1 #4)/phy_4/master}

Type a command below to set path to ‘m’ variable.

% set m [ lindex [ get_service_paths master] 4]

/devices/1SX280LN2S(2|1)|1SX280LN3S1|..@2#1-9.3.2#Stratix 10L SoC Dev Kit/(link)/JTAG/(110:132 v1 #4)/phy_4/master

Type a command below to open a port

% open_service master $m

Type a command below to read UART registers. You can see UART0.cpr, ucv and ctr which are read-only values.

% master_read_32 $m 0xffc02000 64

0x00000046 0x00000000 0x000000c1 0x00000003 0x00000003 0x00000060 0x00000010 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000046 0x00000000 0x00000000 0x00000000 0x00000006 0x00000000 0x00000000 0x00000000 0x00000001 0x00000000 0x00000000 0x00000001 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00083f32 0x3331352a 0x44570110

Type a command below to close the port

% close_service master $m

Best regards,

Yoshiaki Saito

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Hans_1st,

I will close this thread if no further questions from you.

Best regards,

Yoshiaki Saito

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page