- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We work with a CycloneV in active serial configuration mode. The EPCS config flash is connected to the FPGA and also in parallel to an external microcontroller. The idea is to update the FPGA design file in the EPCS flash during runtime with this microcontroller (The microcontroller writes the new configuration to the flash). At the next power-up, the FPGA would then take the new configuration from the EPCS device. In order to programm the EPCS flash during runtime, we need to tri-state the relevant pins on the FPGA (DCLK, nCS...) after configuration. For some reason we cannot chose this option for these pins under "Device and Pin Options/Dual-Purpose Pins" when using CycloneV. With Cyclon IV and Cyclone10 however, this seems to be possible. There is another checkbox called "Enable input tri-state on active configuration pins in user mode" but this seems not to work correctly. Is there anything else we have to pay attention to in order to tri-state these pins after configuration?

Thanks in advance

Regards

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello JSieg4,

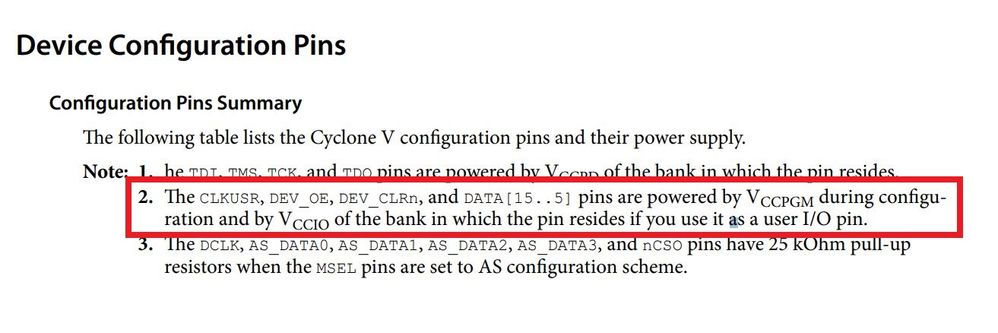

For Cyclone V device, only these pins can use as user I/O pin after configuration:

- CLKUSR

- DEV_OE

- DEV_CLRn

- DATA[15...5]

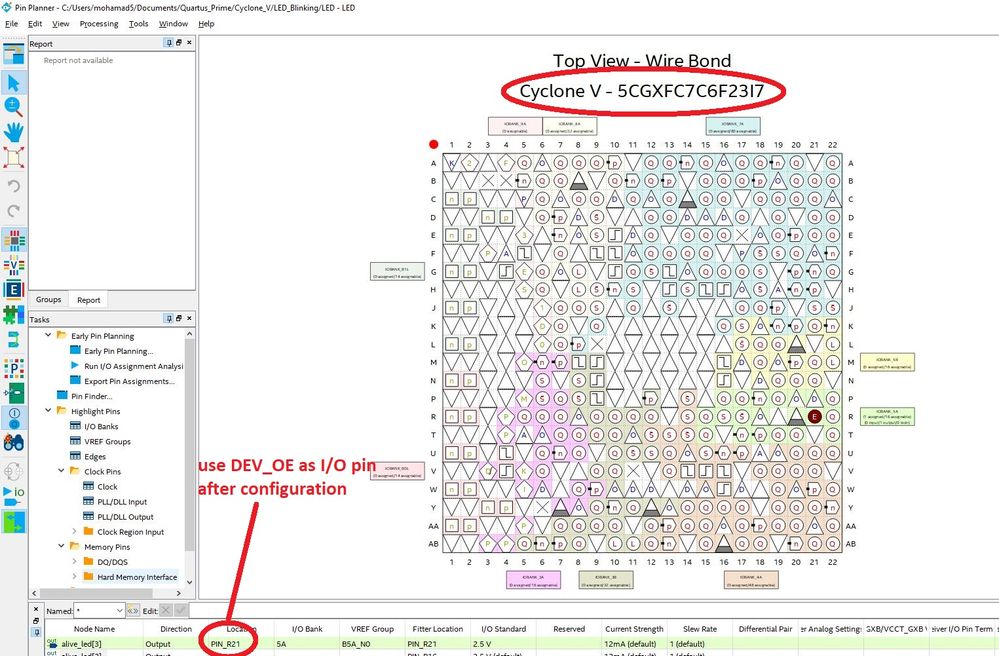

Below is example how I use DEV_OE pin as I/O pin after configuration.

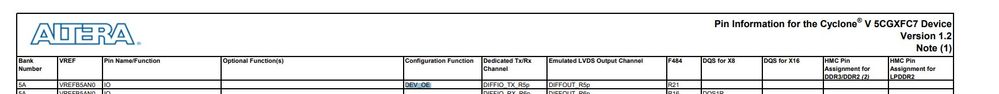

Pin information for Cyclone V device I used:

Others Configuration pins (ie DCLK, nstatus, etc2), you cannot use it as I/O pin after configuration as this pins are dedicated pin.

I hope it is clear now.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Thank you very much for the answer.

OK, i see that the pins can't be used as GPIO's after configuration in Cyclone V devices.

But is there another possibility to tristate them after configuration?

Thanks in advance!

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JSieg4,

possibility to tristate them

What pins you refer to "them"? nstatus pin or any pin?

Cheers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the vague question.

I mean DATA0, nCSO and DCLK.

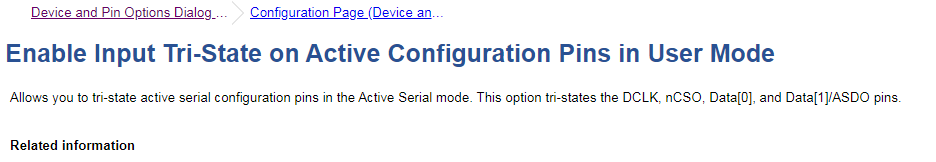

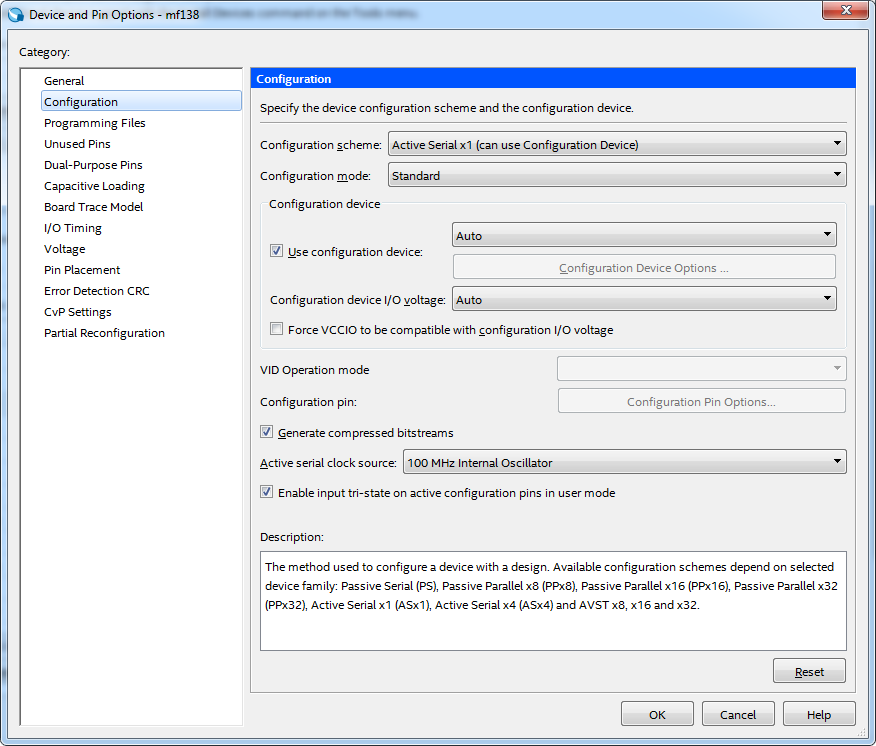

There is this option under: Assignements/Device/Device and Pin Options/Configuration/Enable input tri-state on active configuration pins in user mode

If i understand this link correctly, then this should do the trick

https://www.intel.com/content/www/us/en/programmable/quartushelp/17.0/mapIdTopics/mwh1465495267624.htm

but somehow the pins are not tri-stated even with this option enabled.

We are working with active serial configuration scheme.

I'm using quartus 18.0

regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JSieg4,

If possible, can you send your design?

and also, send the screenshot of "the pins are not tri-stated even with this option enabled."?

I want to duplicated on my side.

Cheers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi WolfGang,

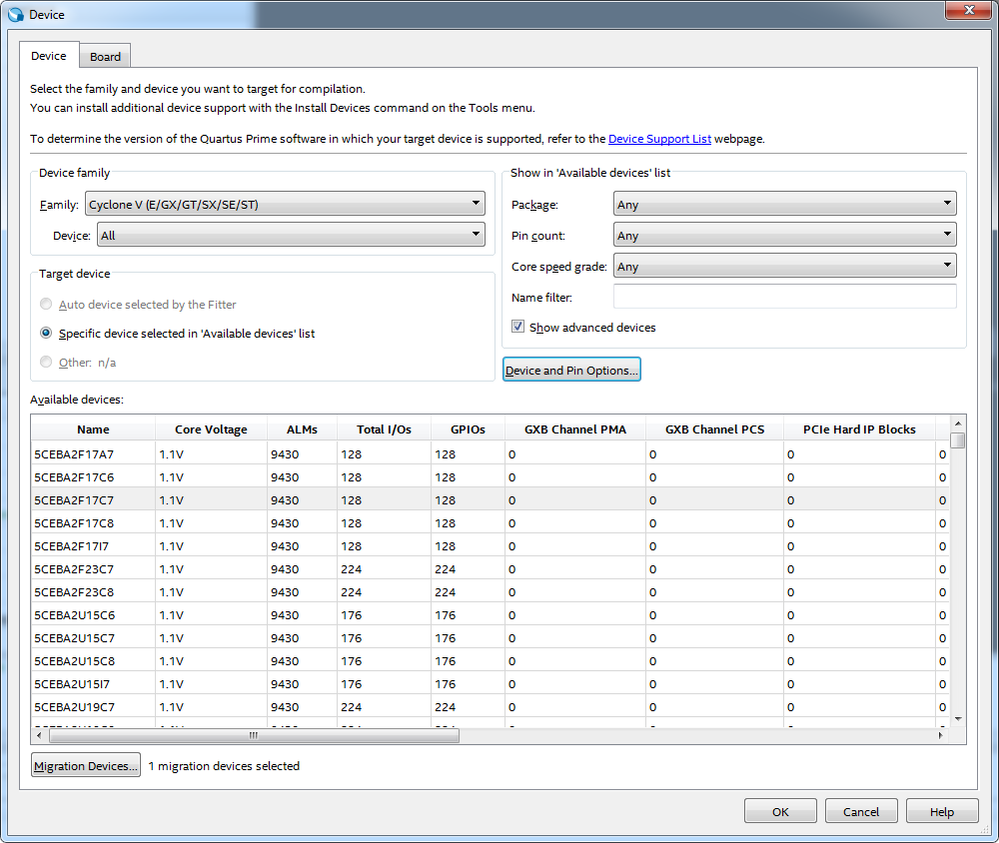

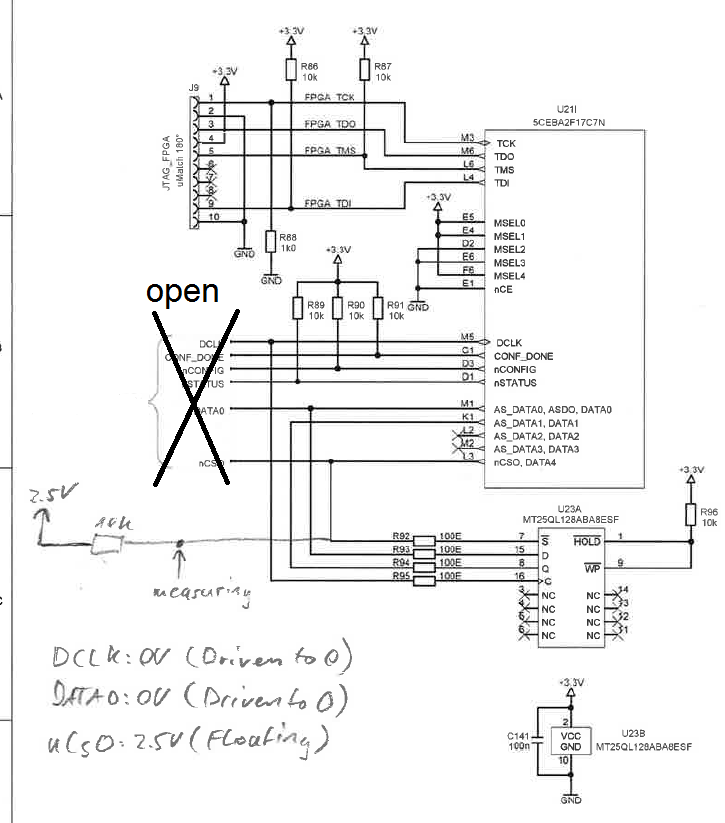

Unfortunately I cannot send you the whole design because it is confidential. But please find the following screenshots.

apart from that we do not use special settings.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JSieg4,

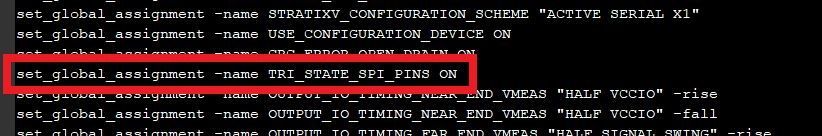

Can you check your .qsf file whether this option is enable or not?

(following assignment indicate this option is enable(red circle) )

One more thing, how do you determine whether this pins ( DATA0, nCSO and DCLK) tri-state or not?

Did you scope the waveform of this pins? if yes, can you share the picture of the waveform?

Cheers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

Thank you for your efforts.

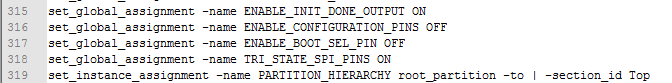

I checked the obtion in the .qsf file (see picture below).

We did not record any waveforms. We just tried to set the pins we wanted to tri-state to a 2.5V potential after configuration.

If they were tri-state we should measure 2.5 V at the point shown in the picture below. But for two of the pins we measure 0V so they seem to

be driven to GND and not tri-state.

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The output will be high or low depending upon its output logic level.

I don't think you can just simply measuring using above circuit to determine whether pins are tri-state or not.

The more practical way to determine is include ASMI Parallel IP (I or II) in your design. Then, if the DCLK, nCSO and DATA pins are tri-stated, these pins will prevent ASMI Parallel IP from working correctly in user mode.

I hope this will help.

Cheers.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page