- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nicholas,

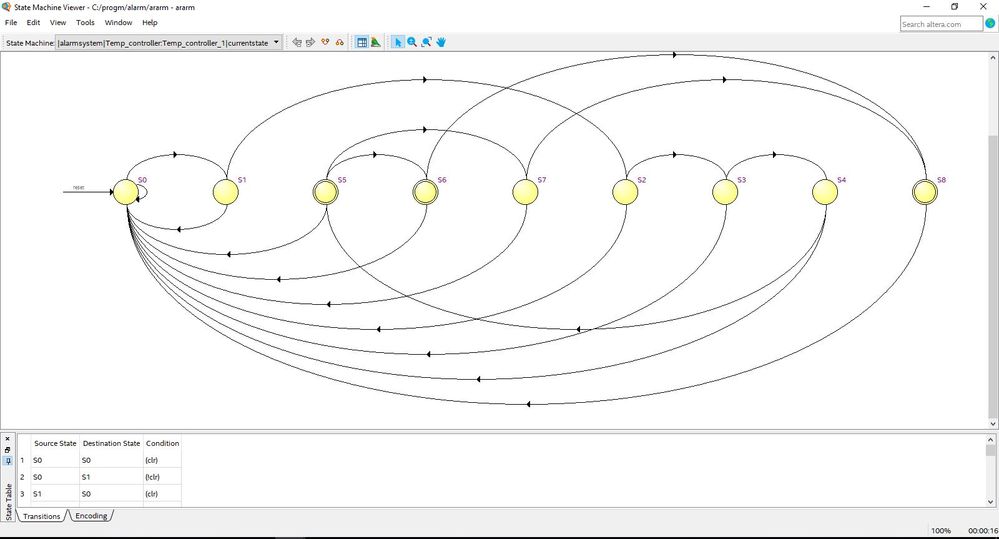

Please provide screenshot of state machine viewer like attached.

=> 'Tool' -> 'Netlist Viewers' -> 'State Machine Viewer'

Regards,

Vikas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

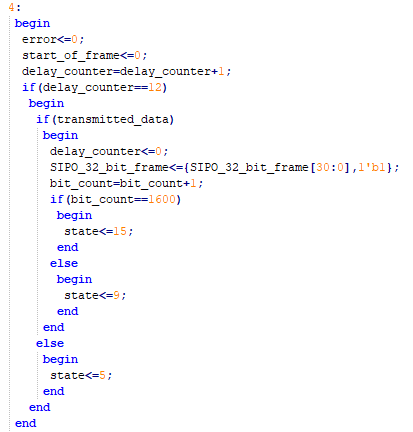

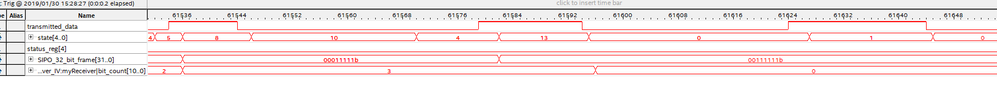

Without seeing your state transition code, it's difficult to figure this out. Decimal 13 is binary 1101, so maybe the most significant bit of your state register is getting set somehow when you want to be going to state 5 (0101).

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page