- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

In power sequencing defined for Cyclone V E,Is there any time period specified between 2 sequences(ie , group 1: +1.1V , group2: +2.5V)?

I have observed the sentence : "Ramp up the power rails in Group 1 to a minimum of 80% of their full rail before Group 2 starts."

No Time difference between sequences is mentioned.

Thanks

Ashad

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Ashad for your inquiry. Let me get back to you after reviewing your question.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ashad

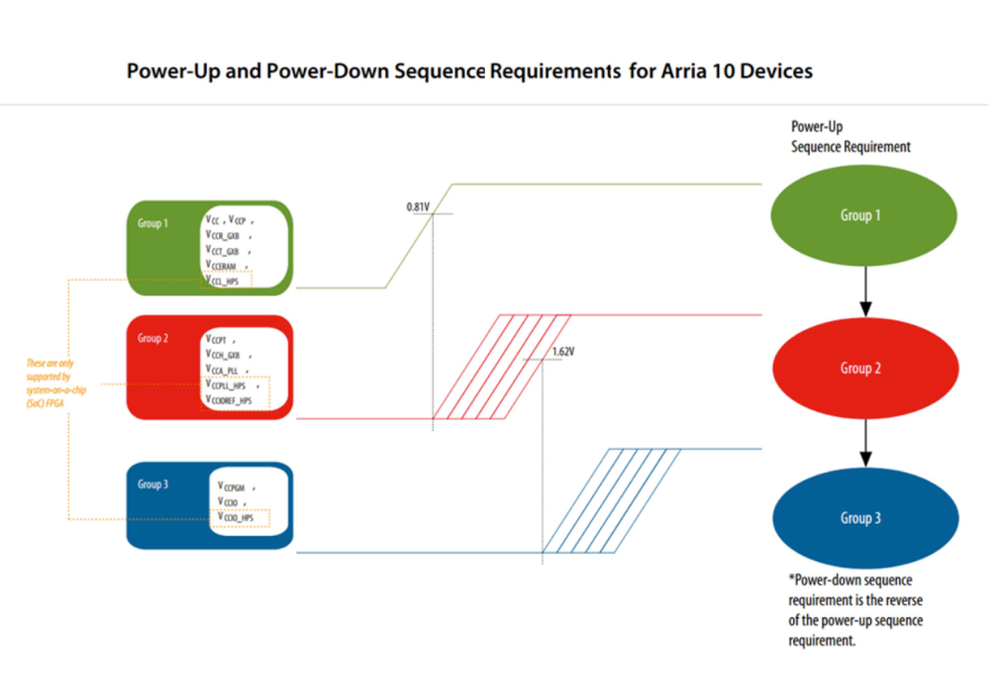

Sorry for late response. For different power rail groups' power up sequence, we need to meet the voltage points requirement in order to meet the spec. I am quoting one of the external site's example diagram as follow (this is for Arria 10 requirement but the same concept applied to Cyclone V devices per Cyclone V spec):

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks @ewO_Intel .

But in cyclone V handbook , only 2 groups are mentioned.

Also no power down sequence mentioned.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ashad

The example diagram above is showing the Arria10 device, we shall refer to the spec for the power rails available in Cyclone V. The recommended power down is in the reverse sequential order of the power up sequence.

Thanks.

Eng Wei

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ashad

Let me know if you still have further inquiry for this topic before we proceed to close the ticket.

Thanks.

Eng Wei

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page