- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Im officially out of luck. After wasting an entire week on trying to get the programmer to work I posting my question within this forum.

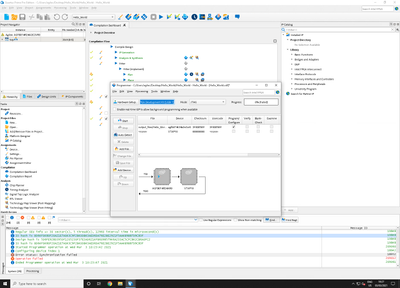

I've got multiple bit stream files I'd like to use for configuration of our agilex FPGA (AGFB014R24A2E3VR0). While the UBII and Power Max 10 chips do seam to work (the board test system shows power and clock stats) the programming (both our bitstream and the intel example bitstreams) always fails at 13% (using both the quartus programmer and the one provided by the BTS). Searching the exact error message (obtained by right click -> copy on the log message) wasn't of any help. We're using Quartus Pro 20.4 on Ubuntu 20 and Windows 10 (neither worked, both with the same issue).

Please review the attached screen shot for further details.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

thanks a lot for your help! We've fixed this issue now. One thing we'd like to share, for a potential future reader, is that in addition to the above mentioned article one needs to completely erase the flash prior to configuring. Our working solutions looks like the following:

- Power off the board. Waiting for the caps to be drained doesn't seam to be necessary.

- Set MSEL[2:0] to ON/OFF/OFF

- Power on the board.

- Erase the boards flash using the programmer tools

- Power off the board.

- Set MSEL[2:0] to OFF/OFF/OFF

- Power on the board

- Programm your *.sof file.

It's also required to leave the JTAG chain in the default configuration while erasing the flash. Last but not least: If step 8 fails retry a couple of times until it stops failing (we usually don't need more than 3 tries). It also seams to be more reliable (programming fails less often) at 24MHz than 6MHz, which the programmer defaults to anyway.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I suspect your TCK frequency might be the root cause here.

Can you kindly try to reduce your TCK frequency to 6 MHz (default value)?

Below link is the command to change TCK frequency (on page 14= "2.8. Changing the TCK Frequency")

Kindly try it out with your design and let me know the result.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you check the following?

- Have you tried to program the agilex with a simple design with SOF bitstream?

Thank You

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't know if it's relevant but we're getting the following warning when trying to program said test-bitstream (which I've attached to this message for reference purposes):

Warning(19729): Current CMF data structure hash (0x15CD440C) is older version than latest CMF data structure but still allowable.

This might be transition period. You should update your CMF to latest version with hash { 0x8AC9CBBA } [ACDS 20.4 Release]

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It should have something to do with Quartus compatibility issue from 19.x to 20.4, which means you probably fail to configure FPGA SOF 20.x again if FPGA has been configured with 19.x image right after power cycle. For devkit, it usually has an image in ASx4 flash for power-on boot-up, so if the AS programming file JIC file generated by 19.x, then it probably runs into FPGA 20.x SOF file configuration issue later on after power cycle. So there are two options to go, one is to erase ASx4 flash with Programmer, the other one is to set MSEL to JTAG only mode. BTW, please do use 19.x Programmer to configure 19.x SOF file, same to 20.x SOF file, otherwise, it may run into configuration issue as well.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can confirm that setting SW1.1 to ON results in a successful load of the SOF after a power cycle.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It seems your analysis is reasonable. I wonder how to erase ASx4 flash with Programmer before the FPGA can be configured. Are there any documents illustrate this operation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May i know which SOF bitstream you are using in the design example? Can you create a simple SOF file with simple input and output initialization and program and see?

Meanwhile for the warning message regarding to CMF, it can be safely ignored.

Thank You.

Regards,

bruce

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

from the BTS we've tried bts_config.sof and qsfpdd_xcvr_nrz_25gbps.sof as well as the GPIO example. The Bitstream we've provided above (Have a look inside Hello_World.tar.xz), initializes the I/O and toggles the GPIO and QSFP leds at 1Hz. Besides writing a bitstream generated by the golden top example, I'm out of Ideas what could be more simple.

Also I observed that sometimes, the first JTAG timeout error message occures prior to the 209060 message indicating the start of the programming process.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you share me the screenshot of the Quartus programmer?

Also, what is the device part number used in the quartus design?

Thank You.

Regards,

Bruce

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We're using the AGFB014R24A2E3VR0 part as stated on the sticker on our dev kit. Since our last post we downgraded to Quartus 19.1 and get a different error since then (Error(18952): Error status: Synchronization failed). I've attached a recent screenshot as requested.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you try to use the previous programmer version that you are using? Also, try to remove the other devices in the JTAG chain and remain only the agilex.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm observing the exact same problem on two (out of two) boards.

Our boards are based upon the AGFB014R24A2E2VR0 device.

The result is the same with a very simple LED flashing design as with a design downloaded from:

For example:

agilexfb_agfb014r24a2e2vr0_fpga_en_reva_v20.4b72_v1.0/examples/pcie_gen4/pcie_gen4_ep_ed.sof

Setting DEVICE_INITIALIZATION_CLOCK INIT_INTOSC does not change the result.

It fails at different TCK speeds, including 6MHz.

Running thousands of IDCODE cycles reports no problems.

Using an external USB Blaster (TerASIC) results in the exact same error messages.

I'm running Quartus Programmer Pro v20.4.0.72 under Ubuntu 18.4

I have no problems loading a sof on a CycloneV SoC board using the same host and SW.

All DIP switches settings are as when the boards were received and according to the default values in the user guide at:

https://www.intel.com/content/www/us/en/programmable/documentation/zbg1567202330317.html

I always get the error:

Error (18950): Device has stopped receiving configuration data

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18947): Device not responding

Error (209012): Operation failed

the first time after power cycle of the board. Then any subsequent programming operations results in:

Error (18939): Unexpected error in JTAG server: Timeout

Error (18939): Unexpected error in JTAG server: Timeout

Error (18952): Error status: Synchronization failed

Error (209012): Operation failed

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Leon,

Can you try to change SW1.1 to ON as per suggested? Any update on this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'll be in office tomorrow and will report my results here.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It seems like we have a solution for this error message (Error(18939): Unexpected error in JTAG server: Timeout.):

Also, after that, can you change the TCK frequency to 6 MHz?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page