- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

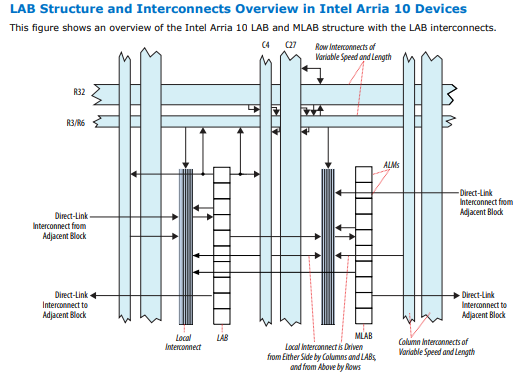

I am working with an Attila board on which is installed an Arria 10 FPGA component. In the Arria 10 handbook, there is a diagram of the LAB structure which is atteched below. I want to know what do R32, R3/R6, C4 and C27 refer to.

Thank you.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This is is the block diagram of a LAB in ARRIA 10 FPGA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your reply. Actually, what I want to know is the meaning of values after the C or R letter. When I read the handbook of Cyclone5 or Cyclone 10 GX FPGA, I find approximately the same diagram. The difference is in the incterconnect. For example:

- Arria 10 : C4, C27

- Cyclone 5 : C2/C4, C12

- Stratix 10 : C2/C3/C4, C16

So, are these values related to the interconnects technology, speed or width...?

Regards,

Lotfi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

C: column, R: row

The number specifies how many device resource blocks (LABs, memory, or DSP) the wire route spans. Longer wires are usually more limited and their overuse can lead to congestion issues. You can highlight wire usage for your design using a report in the Chip Planner. The report generates a heat map so you can see where there are "hotspots" of the overuse of certain wire types.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for the explanation. However, I think that providing long wires enables the routing tool to overcome some bottleneck problems, espicially in nodes with high fanouts. Actually, I am testing a project design on Arria 10, Cycone 10 Gx, Cyclone 5 and Stratix 10 FPGAs. I have got these results:

- Arria 10 and Cyclone 10 Gx : my project frequency can go until 300Mhz

- Stratix 10 : my project frequency can go until 275Mhz (retiming option is disabled)

- Cyclone 5 : my project frequency can go until 160Mhz

For the Cyclone 5, I can understand the results because it is less performant than Arria10, Cyclone 10GX and Stratix 10. However, I was surprised by the timing results for Stratix 10 FPGA because it has an Hyperflex architecture "with registers everywhere".

When I have checked "Lab diagrams" of each FPGA, I noticed that there is a difference in the routing architecture:

- Arria 10 and Cyclone 10 GX : C4, C27, R3/R3, R32

- Stratix 10 : C2/C3/C4, C16, R2/R4/R10, R24

- Cyclone 5 : C2/C4, C12, R3/R6, R14

So do you think that the length of wires can have a negatif effect on the maximum frequency of a project design on FPGA?

Regards,

Lotfi.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If you disable the hyper-retimer in S10, you've removed one of the key advantages from that device, so I don't trust that number at all.

Length of wires is really not something a designer typically needs to concern themselves with unless, as I said, you start running into congestion issues. Turn on the hyper-retimer and try again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Even when I enabled hyper-retimer I didn't get the 300Mhz. The estimated Max frequency is now 280 Mhz. Actually, my project is an architrectural design based on elementary units (registers and logic equations). So, the retimer was not able to boost the frequency as expected. However, I think that I have to change the design so that I can use the full potential of the board (for example replacing multicycle paths with pipes of registers).

Thank you for your help.

Regards,

Lotfi.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page