- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I wrote a custom Avalon MM Master Component that interfaces via Qsys interconnect with a SPI (3 Wire Serial) Intel FPGA IP instance.

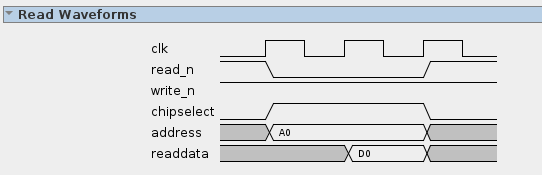

The signals and waveforms specified by the SPI core control port for read transactions are:

I have reflected these in my Avalon MM master Qsys component. Additionally I've included a waitrequest signal, as instructed in the Intel Avalon Interface Specifications documentation:

avm_waveshare_spi_read_n : out std_logic;

avm_waveshare_spi_write_n : out std_logic;

avm_waveshare_spi_chipselect : out std_logic;

avm_waveshare_spi_address : out std_logic_vector (rw_address_width - 1 downto 0);

avm_waveshare_spi_readdata : in std_logic_vector (rw_data_width - 1 downto 0);

avm_waveshare_spi_writedata : out std_logic_vector (rw_data_width - 1 downto 0);

avm_waveshare_spi_waitrequest : in std_logic;

A state machine is driving this signals, in an attempt to read the status register of the SPI core. The address I'm providing for the read is 0x8 (0 + 2*4).

Is there anything obvious I'm missing here? Any hints are much appreciated.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Fixed, it was incorrect size of readdata port and address.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Glad you issue had been solved. I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page