- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Design Background:

HPS (SoC) AXI master (32-bit address) --> Avalon mm bridge (32-bit address) --> Avalon mm slave component (16-bit address). All the three parts are Intel IPs and there is no additional logic in between.

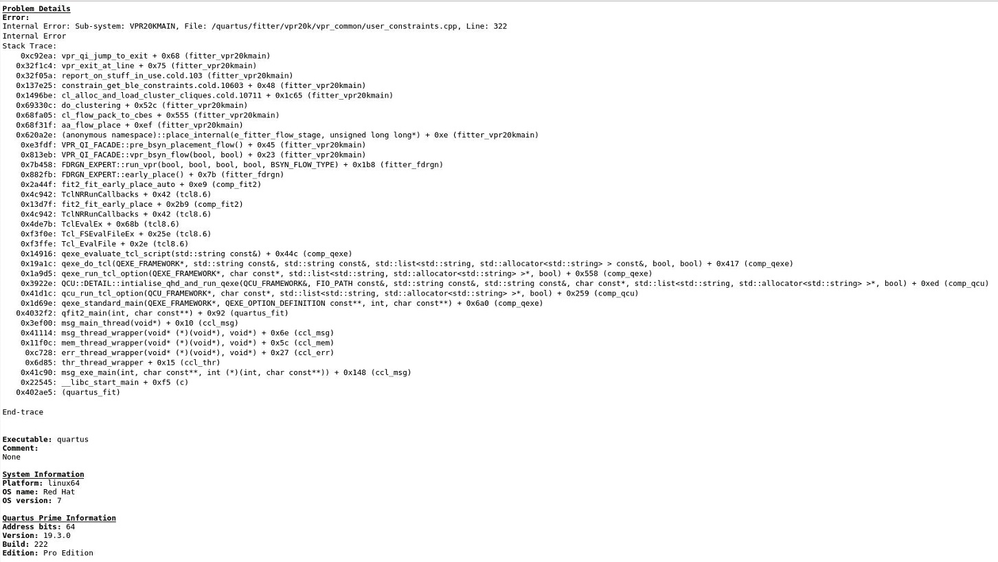

I can successfully compile the design and generate .sof if I simply assigned the lower 16 bits address of Avalon mm bridge master output to the slave component. But due to the slave component IP addresses are word addresses, I need to shift the address to the right by 2 bits. The only change I made in the design is the assignment, using Avalon_mm_bridge_address (17 downto 2) instead of Avalon_mm_bridge_address (15 downto 0). It crashed and got internal error as following:

I have tried to disable the "Perform register retiming", or using "srl" function to go around it but neither methods worked. Has anyone seen the same or similar issue before? How should I fix it? Thanks.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Please let us know whether the below link is helpful to you.

Thanks and Regards

Anil

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page