- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

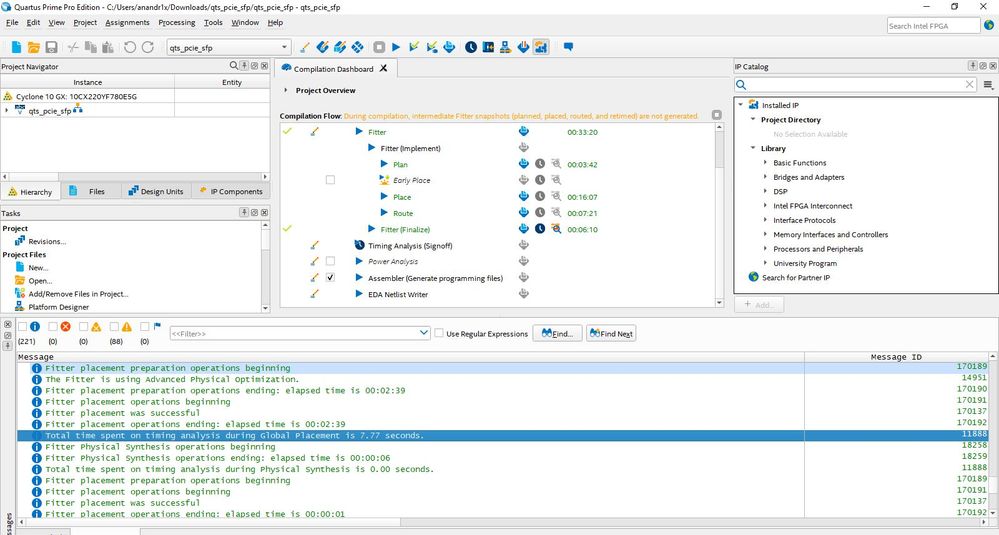

I'm currently experimenting on the qts_pcie_sft project.

The unzipped qts_pcie_sft project doesn't compile on 19.2. Error on Board Trace Model setting on some pins i can't identify. Couldn't find any info on the error codes.

Tried 17.1 because the source files appears to have been developed using version 17 but Quartus quits/stops when i click on compile right after finishing IP Generation during compile process.

I'm using uneditted sourcefiles. So i'm stuck at the moment. I need to prove first if the source files are working before i can add on our custom codes. Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Apologies for delay

We have to remove remove Board trace models.

Please remove below lines from .qsf file and run full compilation.

set_global_assignment -name OUTPUT_IO_TIMING_NEAR_END_VMEAS "HALF VCCIO" -rise

set_global_assignment -name OUTPUT_IO_TIMING_NEAR_END_VMEAS "HALF VCCIO" -fall

set_global_assignment -name OUTPUT_IO_TIMING_FAR_END_VMEAS "HALF SIGNAL SWING" -rise

set_global_assignment -name OUTPUT_IO_TIMING_FAR_END_VMEAS "HALF SIGNAL SWING" -fall

Checked with Quartus pro 19.1

Regards

Anand

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Issue with long folder/file path. Reduced the number of folders and compilation proceeded partially but still with errors.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please user reference design from below link

https://forums.intel.com/s/createarticlepage?articleid=a3g0P0000005QyOQAU&action=view

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_c5_pcie.pdf

https://forums.intel.com/s/createarticlepage?articleid=a3g0P0000005RSyQAM&action=view

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anand,

We will be using Cyclone 10 to replace our existing Cyclone V based product. I was hoping for a starting project for a Cyclone 10GX development board.

Update:

- on 17.1, regenerating all the QSYS files helped a bit, compilation reached 35% before Quartus hangs.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Anand,

This might be the same issue. See link

I curently have it @ f:/sandbox/qts_pcie_sft/qts_pcie_sfp. I'll reduce it to just 1 directory tomorrow and see if it compiles.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Reducing project directory tree to f:/qts_pcie... didn't help. 17.1 compilation still hangs while 19.2 compilation still results with these errors:

Error(329006): Some pins have illegal board trace models.

Error(20403): Global setting for OUTPUT_IO_TIMING_NEAR_END_VMEAS is not supported. Please use this setting with pin assignments.

Error(20403): Global setting for OUTPUT_IO_TIMING_FAR_END_VMEAS is not supported. Please use this setting with pin assignments.

...

How can i fix these fitting errors?

A fresh download of the Cyclone 10 GX development board collateral which contains the qts_pcie example project resulted in the same compilation issues. Is there an upgraded/fixed project?

In case it matters, i'm using a Windows 10 Pro 64 bit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joel,

Yes, i have faced same issue in compiling using Quartus pro 19.1. let me check and come back.

Please try design from design store.

https://fpgacloud.intel.com/devstore/platform/?acds_version=any&ip_core=PCIExpress&board=102

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Apologies for delay

We have to remove remove Board trace models.

Please remove below lines from .qsf file and run full compilation.

set_global_assignment -name OUTPUT_IO_TIMING_NEAR_END_VMEAS "HALF VCCIO" -rise

set_global_assignment -name OUTPUT_IO_TIMING_NEAR_END_VMEAS "HALF VCCIO" -fall

set_global_assignment -name OUTPUT_IO_TIMING_FAR_END_VMEAS "HALF SIGNAL SWING" -rise

set_global_assignment -name OUTPUT_IO_TIMING_FAR_END_VMEAS "HALF SIGNAL SWING" -fall

Checked with Quartus pro 19.1

Regards

Anand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That worked! Thanks Anand!

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page